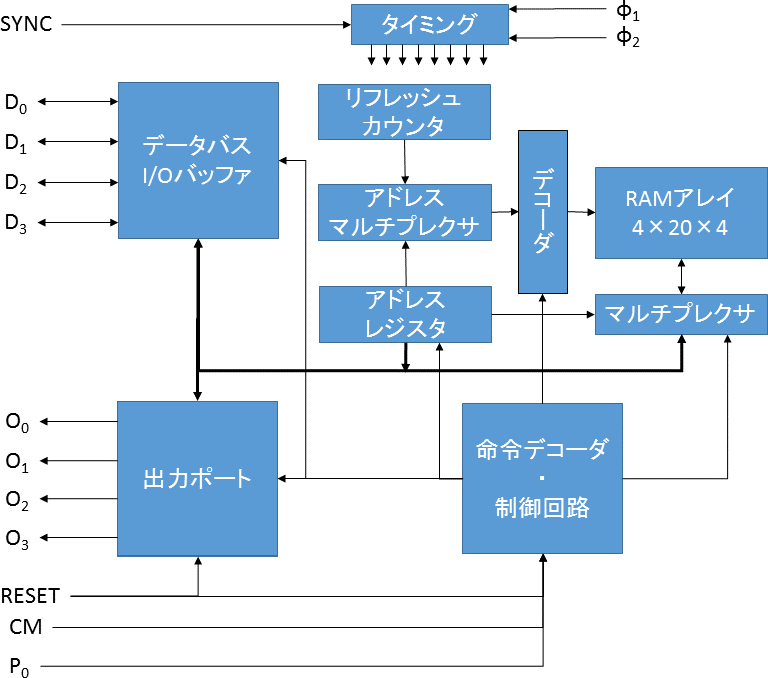

下に4002のブロック図を示します.この図を使って4002の内部について説明します.

タイミングとデータバスI/Oバッファについては4001などと同様です.詳しくはこちらをご覧ください.

次にリフレッシュカウンタ,アドレスマルチプレクサおよびアドレスレジスタについてまとめて説明します.一言でいえば,これらはすべて4002の記憶方法がダイナミックRAMであるために必要な回路です.ダイナミックRAMではコンデンサに貯められる電荷の有無で0と1を表現していますが,電荷は時間がたつと漏れていってしまう性質がり,それを回避するため定期的にリフレッシュしなければなりません.そこで,リフレッシュを一定周期に行うため,タイミングからのクロックをカウントするのです.これがリフレッシュカウンタの役割です.さらにアドレスレジスタで指示されたコンデンサの電荷をチャージするようになっており,そのアドレスを指し示すRAMの場所に対してリフレッシュを行うようにするためにアドレスマルチプレクサが必要なのです.

次に出力ポートです.あらかじめSRC命令で指定された4002にある出力ポートから,WMP命令でデータを出力することができます.

最後に命令デコーダ・制御回路,マルチプレクサそしてRAMアレイの説明をします.SRC命令ではX2およびX3のタイミングで4[bit]ずつ,計8[bit]の情報をRAMに送ります.この情報には下の表で示す内容が含まれています.

| X2 | X3 | ||||||

| D3 | D2 | D1 | D0 | D3 | D2 | D1 | D0 |

| チップ番号 | RAMアレイ番号 | メインメモリ文字番号 | |||||

| (0~3) | (0~3) | (0~15) | |||||

まず,X2は上位2[bit]と下位2[bit]に分けられ,上位2[bit]によりチップ番号,下位2[bit]により4002のRAMアレイ番号が指定されます.そしてX3の4[bit]によりメインメモリ文字番号を表しています.チップ番号とP0および4002の種類の関係を下表で説明します.なお,D3とD2はともにX2のときのものです.例えばD3=1,D2=0のときには4002-2かつP0=VSSのものが選ばれます.

| チップ番号 | 4002の種類 | P0 | D3 | D2 |

| 0 | 4002-1 | VSS | 0 | 0 |

| 1 | 4002-1 | VDD | 0 | 1 |

| 2 | 4002-2 | VSS | 1 | 0 |

| 3 | 4002-2 | VDD | 1 | 1 |

以上のように,SRCのX2およびX3で送られてくる情報をデコードします.さらにそれだけでなく,M1サブサイクルのとき,4001から4004に送られるオペコードが1110(入出力命令)のとき,4004はCM-RAMxをM2(オペラランドを送っているサブサイクル)のときアサートし,4002はそのオペランドをデコードします.例えば,WRM(メインメモリに4004のアキュムレータの値を書き込む)とWMP(4002の出力端子から4004のアキュムレータの値を出力する)を区別するために,4002ではオペランドをデコードしています.

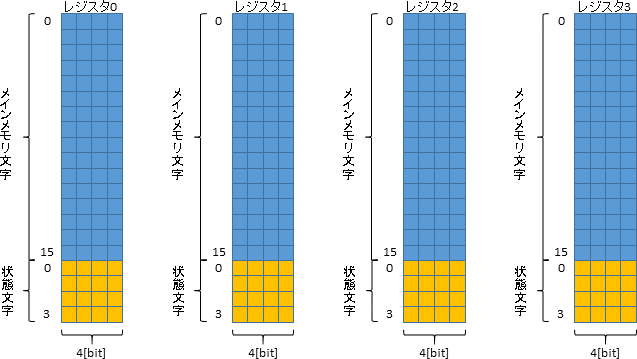

レジスタ番号とメインメモリ文字番号については下の図をご覧ください.下図は1個の4002に含まれるRAMアレイです.このように4個のレジスタが入っています.各レジスタには20個の4[bit]RAMがあり,そのうち16個がメインメモリ文字です.0~15までの番号が振られています.

このように,SRC命令でどのRAMの,どのレジスタのどのメインメモリ文字に対して読み書きするか指定することができます.しかしこのままではどのグループかまでは指定していません.これを行うのがDCL命令です.この命令によりCM-RAM0~3のいずれかをHighにすることができます.従いまして,RAMにアクセスする前段階ではSRC命令とDCL命令を行う必要があると言えます.ここまでお膳立てしたのち,WRM命令でメインメモリ文字にデータを書き込むことができ,RDM命令でデータを読み込むことができるのです.