この文書では,xilinx社製FPGAであるXC6SLX9-2TQG144C(シリーズ名はSpartan6)上に,Verilog HDLによるごく簡単な回路の構築方法について説明します.はじめてFPGAを使う方のために書きますので,なれた方にはまわりくどい箇所もあろうかと思いますがご容赦ください.

次に示す事項を行えるようになります.

- 表示基板にあるLED1を点灯,LED2を消灯させることができます.

- xilinx社製ISEのプロジェクトを作成できます.

- Verilog HDLのソースコードをプロジェクトに追加できます.

- ユーザ制約ファイルにFPGAの端子の入出力および電圧を設定できます.

- PROMに回路情報をダウンロードできます.

環境設定

xilinxのFPGA,とりわけシリーズ7より古いFPGA,たとえばSpartan6上に回路を構築するには,ISE デザインツールというIDE(統合開発環境)が必要です.なお,この文書では触れませんが,シリーズ7以上ではVivadoデザインツールという統合開発環境を用います.さて話を戻します.ISEには無料で利用できるものと有料のものがあります.それらの違いは,対応するデバイスや,IPコア(Interectual Property core)の有無にあります.IPコアとは,何かしらの機能,たとえばSRAMの制御回路を実現するコードのことを指します.ソフトウェアに例えるなら,さしづめライブラリです.この文章で説明しようとしているLEDを点灯させるコードでは当然IPなどは必要ではありませんし,使用したいSpartan6はごく一般的なものですので,無償版のISE Web PACKで十分です.このアプリをダウンロードするにはxilinxのアカウントを作成する必要があります.詳しくはこちらのページを読んでください.なお,ISEデザインツールは,既に過去のデバイスしか対応していないため,保守ライフサイクルに入っています.つまり,今後新しい機能を搭載したISEは登場しないということです.もし,シリーズ7のデバイスを開発対象にするのであれば,Vivadoデザインツールをお使いください.

新規プロジェクトの作成

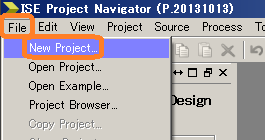

次にISEデザインツールで新しいプロジェクトを作成する方法を説明します.まずはISEを立ち上げてください.するとISEのメインウィンドウが表れますので,下の図のようにFileメニューの中のNew Projectを選択してください.

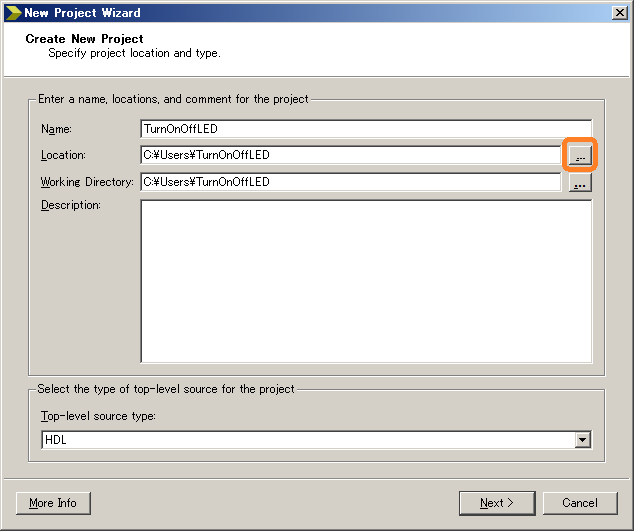

次にプロジェクト名とプロジェクトの設置場所を設定します.今回のプロジェクトをTurnOnOffLEDとしますので,Nameにそれを入力します.その後,保存先を指定します.初期状態では,保存先であるLocationにはC:\Usersが設定されており,この場合,管理者としてISEを実行していなければ保存することができません.また,パスの一部に日本語が入っている場合,管理者であっても正しく保存できません.Windowsにログインしているユーザのドキュメントディレクトリに保存してもよいのですが,ユーザ名が日本語である場合も考えられますので,この文書では誰でも書き込むことのできるC:\Tempの下にプロジェクトを保存することにします.下の図のようにLocationの右端にあるボタンを押してください.

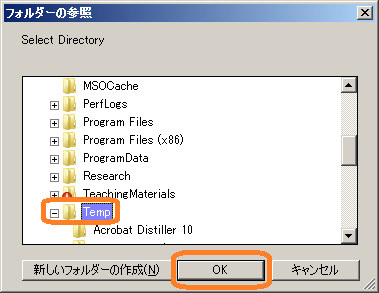

下の図のようにCドライブにあるTempフォルダを指定します.その後,上に示したダイアログにフォーカスが戻りますので,Nextボタンを押してください.

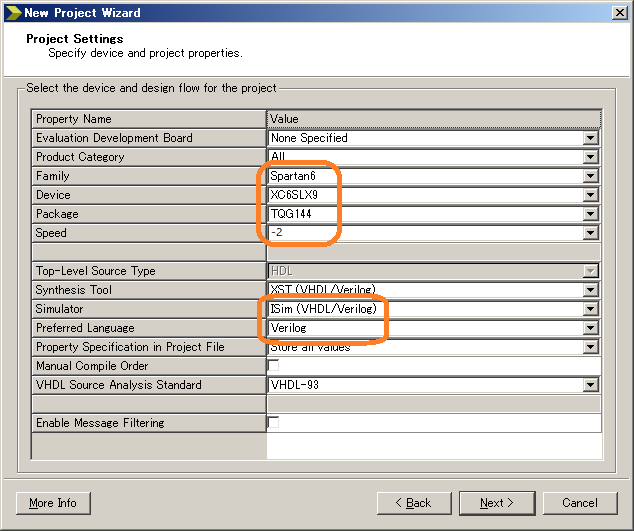

次にターゲットデバイス,使用言語およびシミュレータを選択します.今回使用するXC6SLX9-2TQG144CはFamilyがSpartan6,DeviceがXC6SLX9,PackageがTQG144,Speedが-2を指定します.さらにSimulatorとしてISim,Preferred LanguageとしてVerilogを指定します.下の図はそれらの設定をした様子を表しています.次に進むためNextボタンを押してください.

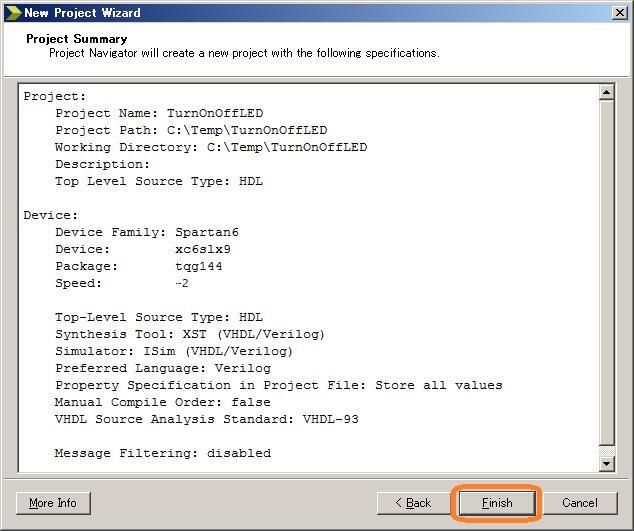

プロジェクトを作成するための設定が終わりましたら,下のようなサマリーが現れます.内容を確認しFinishボタンを押してください.

Verilog HDLコードファイルの追加

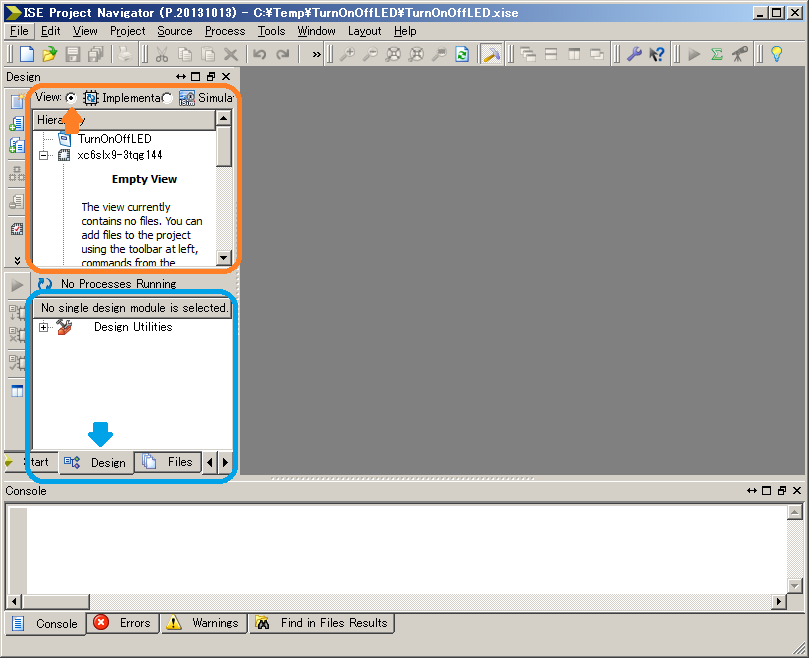

プロジェクトを作成した後に,Verilog HDLのコードファイルを追加しましょう.まずは下の図をご覧ください.左上にある,オレンジ色で囲った領域には,Verilogのモジュールやユーザ制約ファイルが階層構造で表示されます.便宜上,この文書では階層ビュアーと呼びます.階層ビュアー内の上部にはImplementationラジオボタンとSimulationラジオボタンがあります.その名のとおり,回路を実装をするときにはImplementation,シミュレーションするときにはSimulationを選択すると,それぞれにあわせたモジュールなどの表示となります.

左下にある青色で囲った領域には,論理合成や生成した回路構造を見るなど,操作を行うアイコンが表示されます.この領域を操作タブと呼びます.なお,階層ビュアーに表れるモジュールやユーザ制約ファイルにより操作タブに表れる操作項目は変わりますので注意してください.

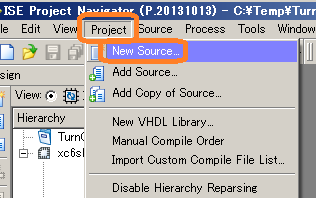

ではVerilog HDLのソースを追加しましょう.ProjectメニューにあるNew Sourceを選択してください.

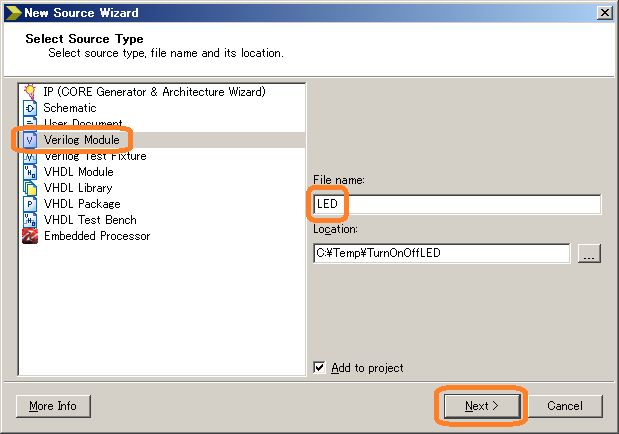

新しくソースを追加するとき,下記のようなウィザード用ダイアログが現れます.ここではVerilog Moduleを選択し,モジュール名と同じになるファイル名を入力します.今回,モジュール名をLEDとすることとします.

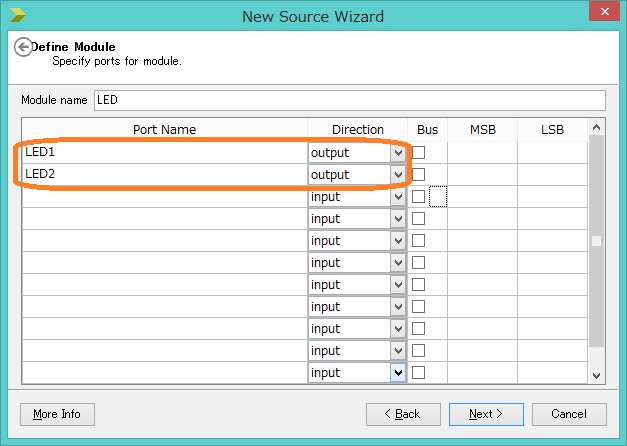

Verilogのモジュールを追加した場合,続いてポートの設定をすることができます.下図のようにポート名(Port Name),入出力方法(Direction)を設定します.もし,ポートがバスである場合にはBusにチェックを付け,さらにMSB(Most Significant Bit)とLSB(Least Significant Bit)の番号を入力します.なお,ポートの設定をVerilogのソースを編集するときに手動で入力することもできます.

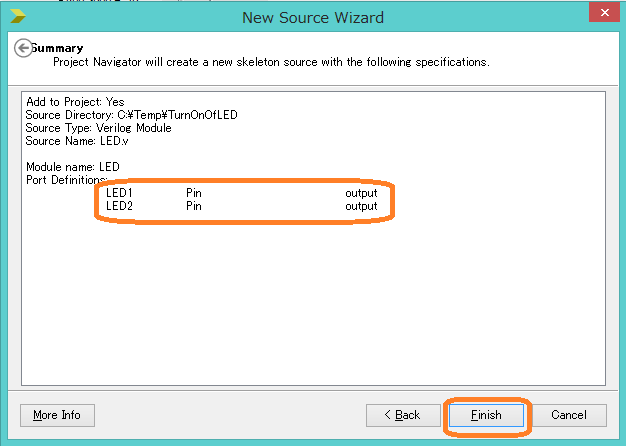

Verilog HDLのモジュールを追加し終えますと,下に示すダイアログが現れます.内容を確認し,Finishボタンを押してください.

ソースコードの入力

次にVerilog HDLのソースコードを入力しましょう.今回実現しようとしている回路では,LED1を点灯,LED2を消灯させます.LED1のカソードがFPGAの114番ピンに,LED2のカソードが121番ピンに接続されており,LED1および2のアノードがVccに接続されていきますので,ポートLED1からLowつまり0を出力すればLED1は点灯し,ポートLED2からHighつまり1を出力すればLED2は消灯します.

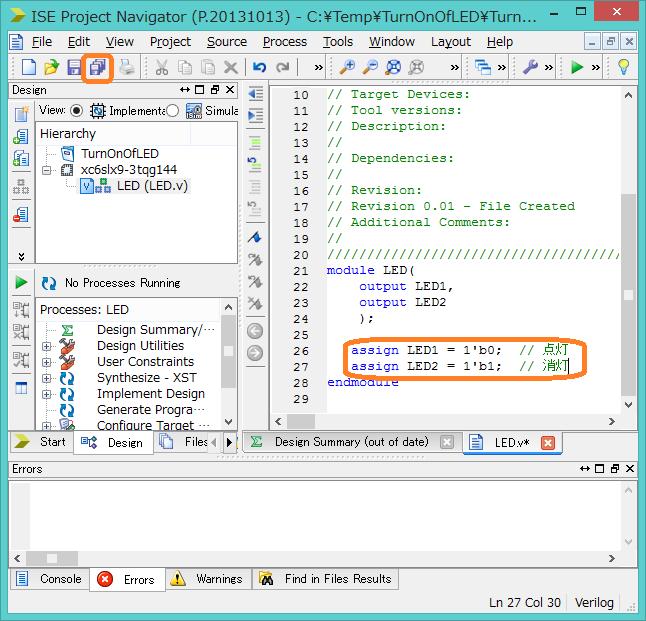

下図は,LED1ポートから0を,LED2ポートから1を出力するコードを書いています.Verilogにおいてあるポートから信号を出力するとき,assign文を用います.LED1に対しては0を出力しており,その0を表す数値として「1'b0」と書いてあります.これは「1ビットの2進数である0」という意味です.

26,27行目にあるassign文を記述しましたら,左上にある,すべてを保存するアイコンを押してください.

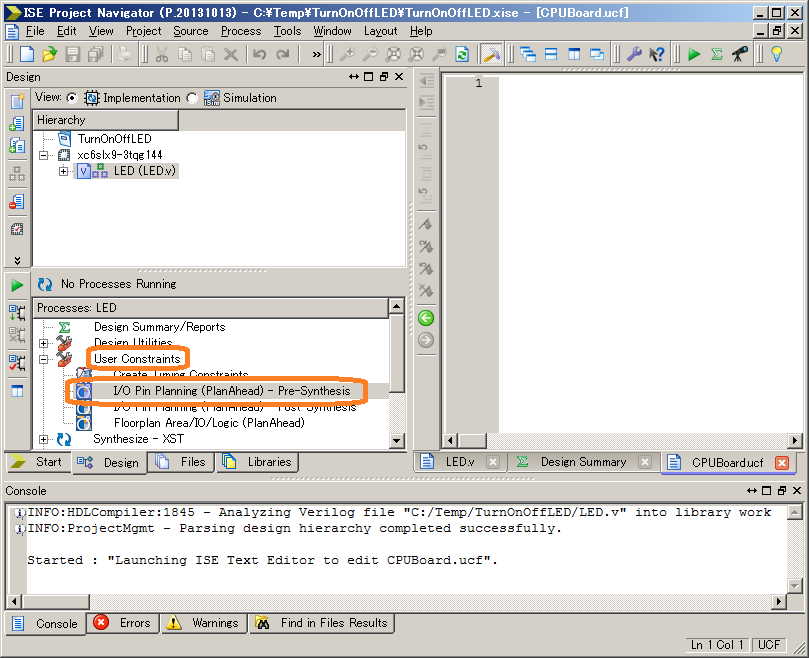

ユーザ制約ファイル(以下ucfファイル)をテキストエディタを使って記述もできますが,ここではPlanAheadというグラフィカルエディタを使ってみましょう.このエディタを使えば,ucfファイルの構文を知らなくてもさまざまなことを記述することができます.下の図のようにUser Constraintsの中にあるI/O Pin Planning(PlanAhead) - Pre-Synthesisをダブルクリックしてください.

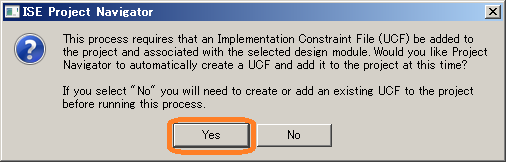

ucfファイルを変更してもよいですか,と問い合わせがありますので,ここではYesを選択してください.

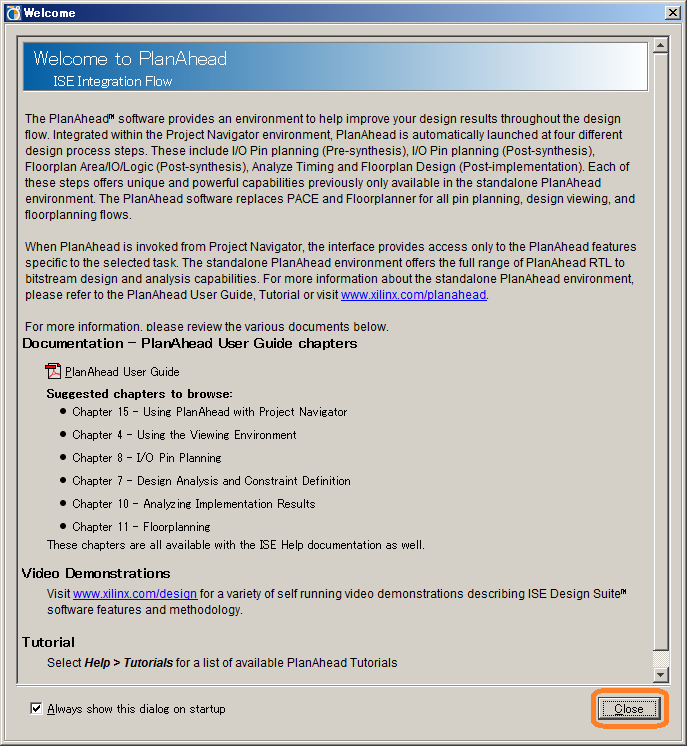

オープニングメッセージとして下に示すウィンドウが現れます.詳しい説明が記されたPDFを読むことができますので,PlanAheadに慣れてきましたら読んでください.

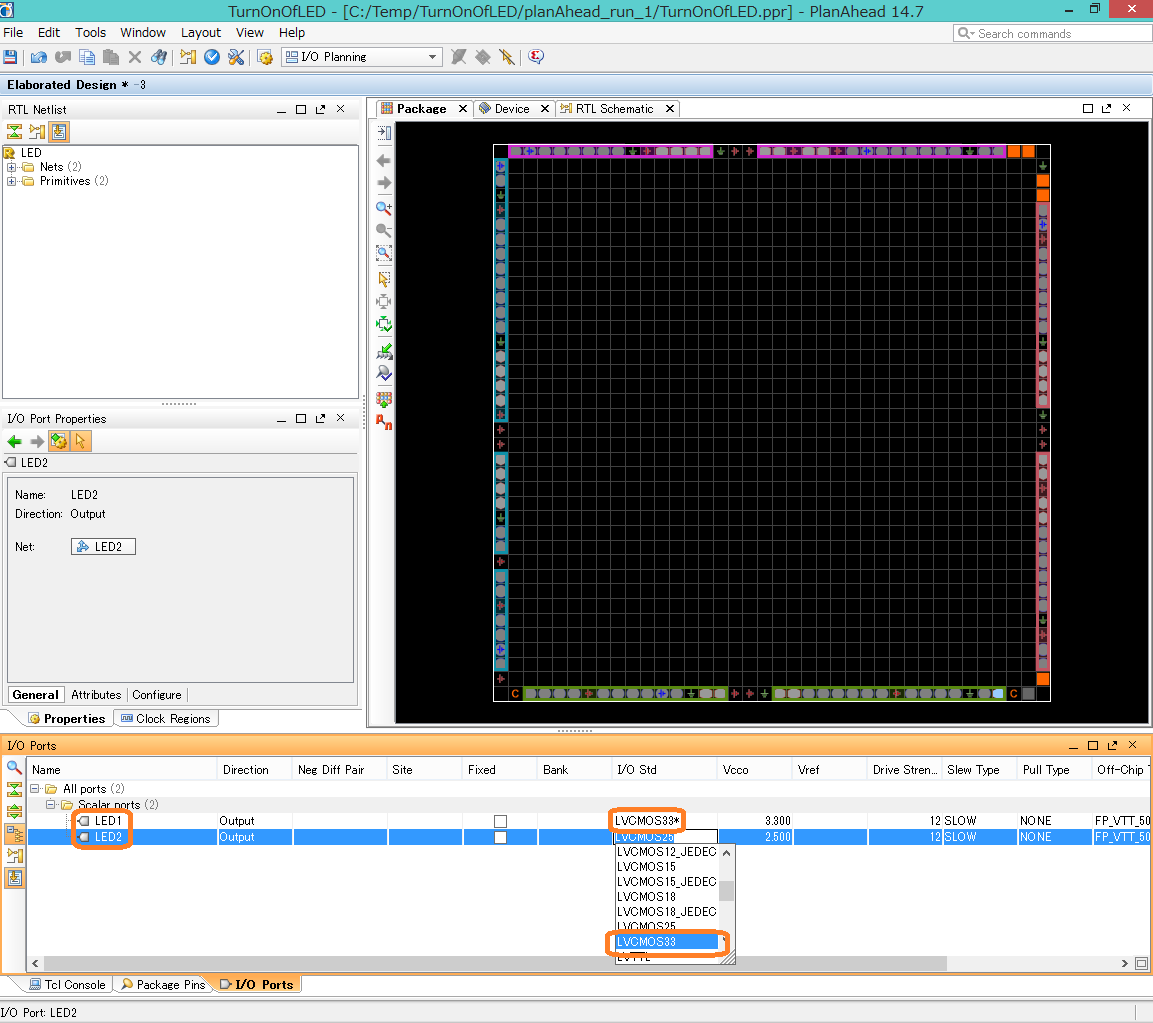

PlanAheadが起動しますと下図のウィンドウが開かれます.まずは出力するレベルをCMOS3.3Vにしましょう.下側にあるScalar PortsからLED1を選択し,I/O Stdにある選択リストからLVCMOS33を選びましょう.同様にLED2に対しても同じことを行ってください.

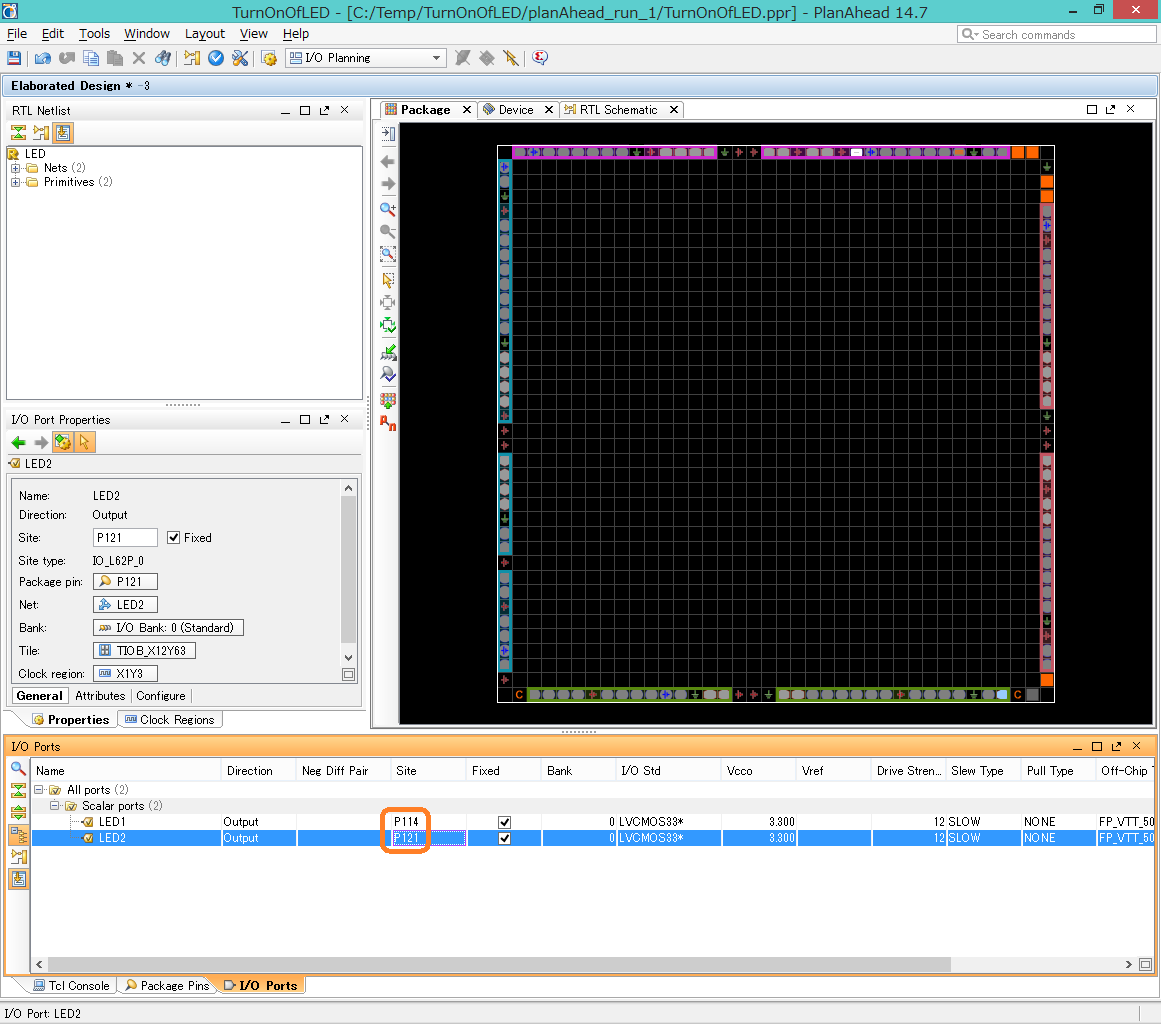

次にLED1をFPGAの端子に接続するための設定をします.LED1はFPGAの114番ピンに接続されていますので下図のようにSiteをP114にします.同様にLED2はP121にしてください.

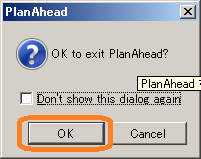

以上でPinAheadによるユーザ制約ファイルの編集は終わりです.保存ボタンを押し,ウィンドウを閉じると下記のダイアログが表れますのでOKを押してください.

FPGAへの書き込み

Verilog HDLのソースコードとユーザ制約ファイルの編集が終わりましたので,次にFPGAへ書き込んでみましょう.事前にダウンロードケーブルをCPUBoardに接続してください.接続方法はこちらをご覧ください.接続しましたらACアダプタを接続し,電源を入れてください.この方法についてはこちらをご覧ください.

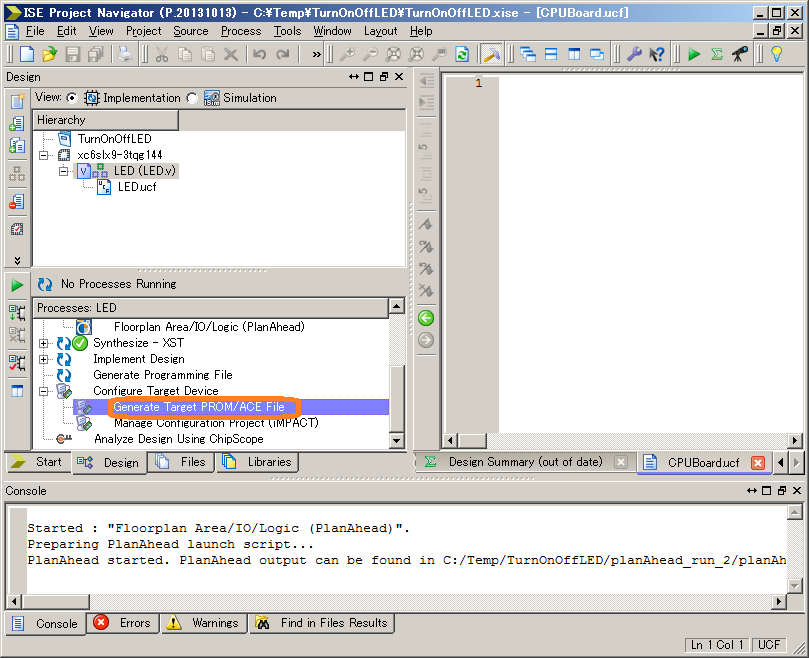

まずは論理合成やフィッチングを行い,ダウンロードファイルを生成します.下図のようにConfigure Target DeviceにあるGenerate Target PROM/ACE Fileを選びますとダウンロードファイルを生成するための各処理をすべて行ってくれます.

ダウンロードについて,独立したプロジェクトとして扱うことができます.そのプロジェクトファイルがまだないことを警告するダイアログが表れますのでOKを選択してください.

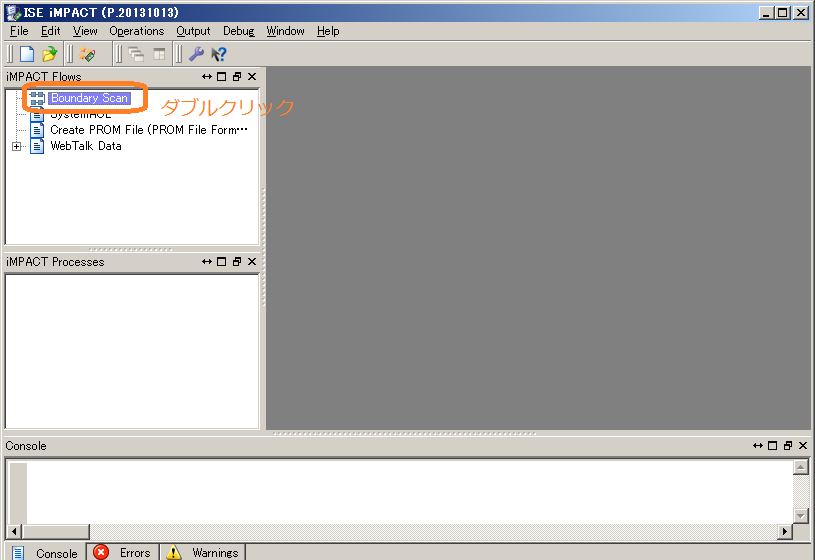

下図はダウンロードするとき用いられるiMPACTです.まずは左上部にあるBoundary Scanをダブルクリックして下さい.

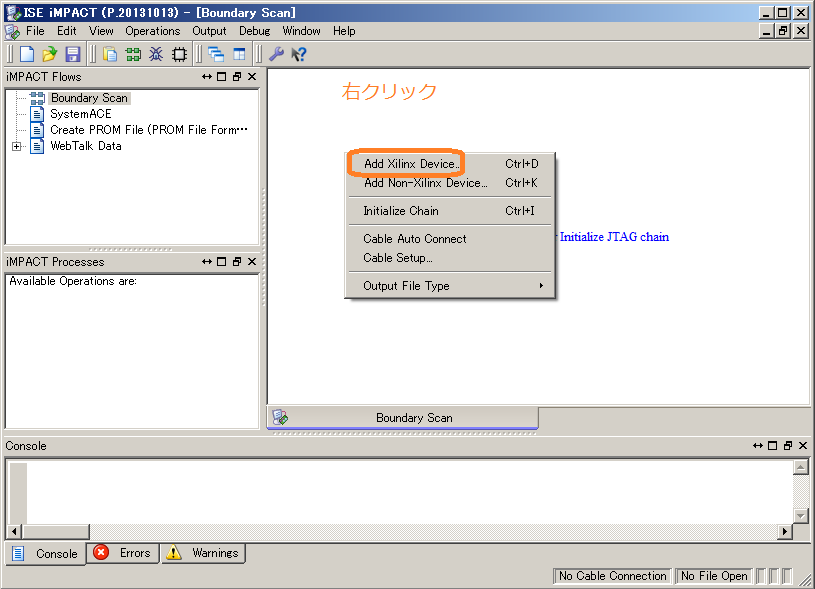

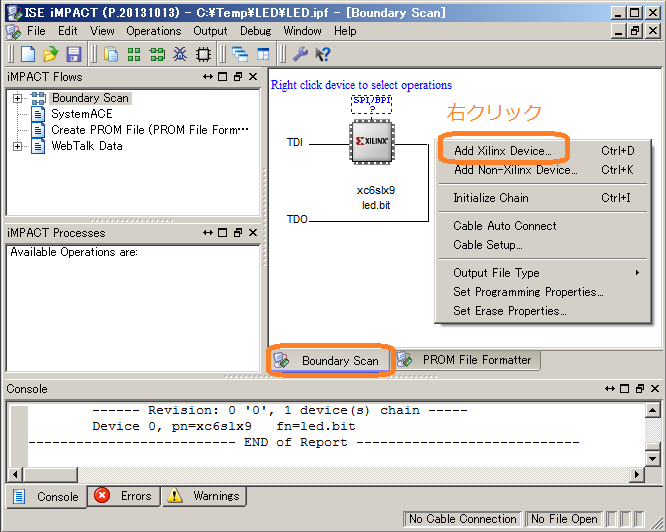

次に段ロードするファイルを選びます.下図のように空白部分を右クリックするとポップアップメニューが表れますのでAdd Xilinx Deviceを選択してください.

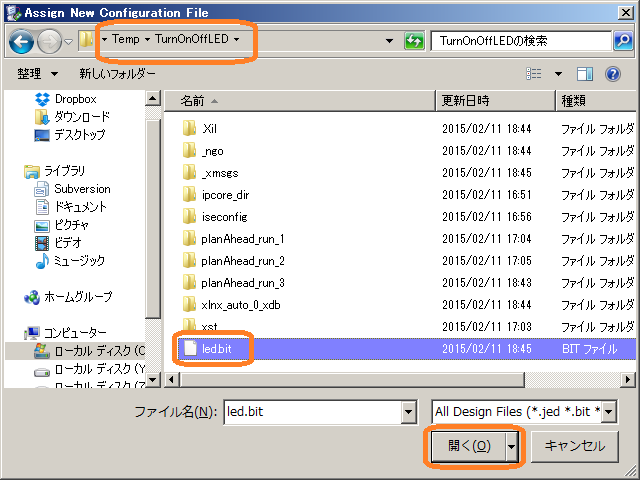

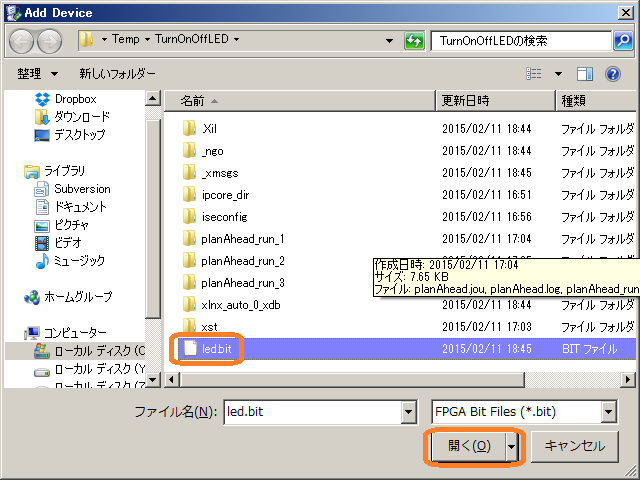

TurnOnOffLEDフォルダへ移動し,その中にあるled.bitファイルを選んでください.

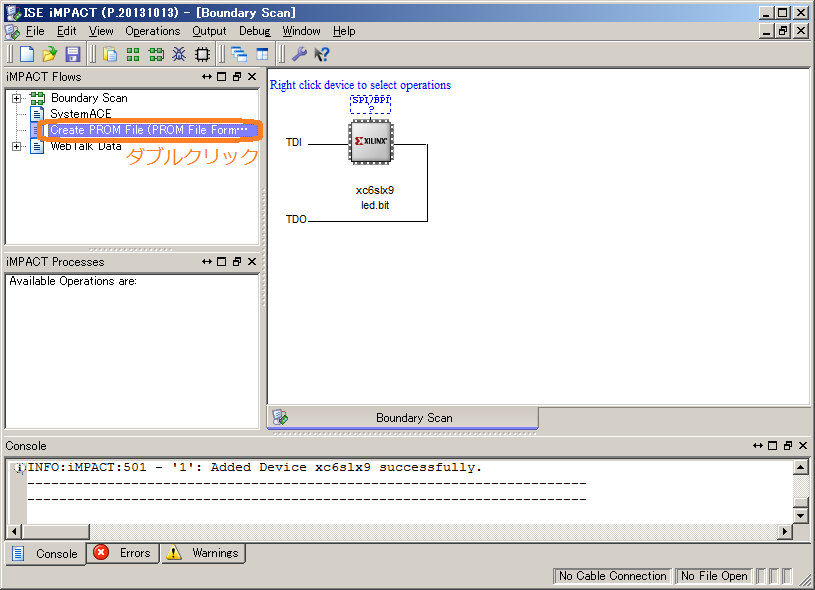

bitファイルを追加しますと,下のようにFPGAのアイコンが現れます.このままでは,FPGAへのダウンロードはできますが,FPGAの電源を切るとダウンロードした情報が消えてしまいます.そこで,PROMにダウンロードファイルを入れることにします.これにより電源投入時にPROMからFPGAに回路情報をダウンロードされるようになります.そのために下図左側のCreate PROM Fileをダブルクリックします.

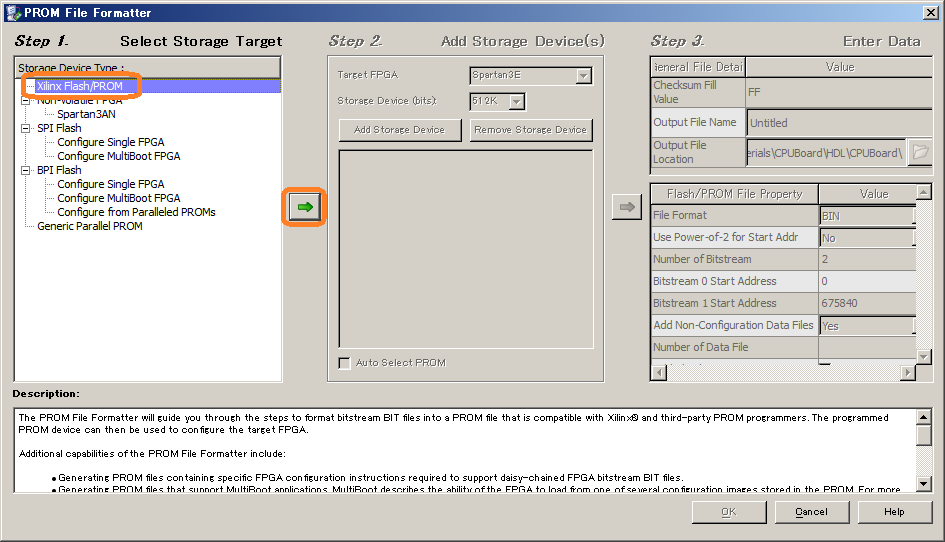

下の図はbitファイルをもとにPROM用ファイルを生成するPROM File Formatterです.拡張子MCSというファイルを生成します.左側にあるXilinx Flash/PROMを選択し,右矢印を押します.

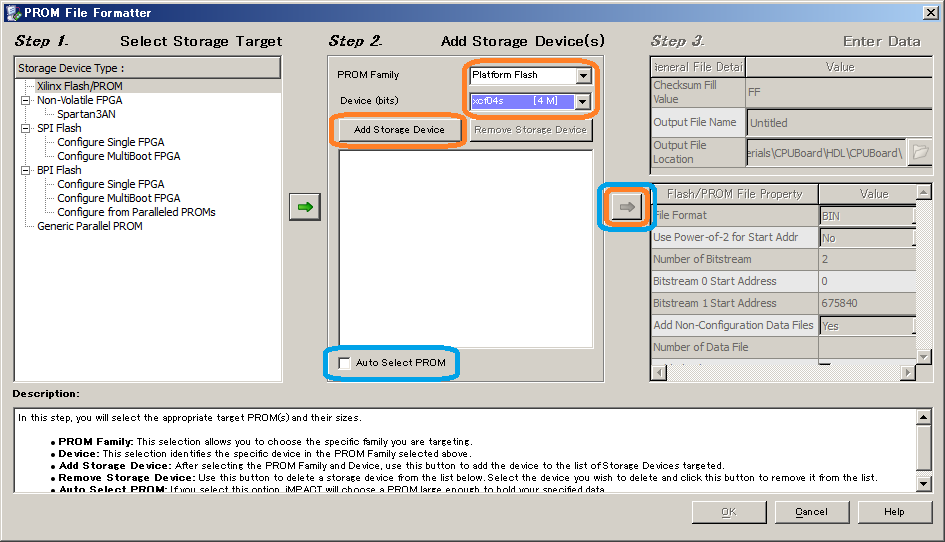

次にPROMの種類を選びます.今回使用しているのはxcf04sですので,下図のオレンジ色で囲った箇所のようにデバイスを選択したのち,Add Storage Deviceを押し,最後に右矢印を押します.このほかの方法として,ダウンロードケーブルと接続されている場合には自動的にPROMを認識させることも可能です.その場合には,下図の水色で囲った箇所のようにAuto Select PROMにチェックを入れたのち,右矢印を押します.

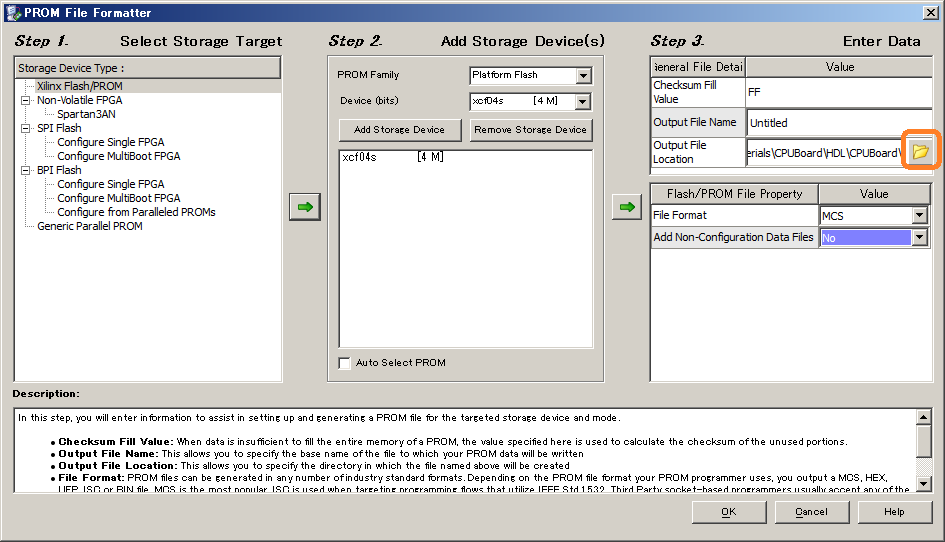

PROM File Formatterで行う最後の手順は,出力するファイルの保存場先とファイル名を指定することです.下図のように右端にあるフォルダアイコンを押し,保存先を指定します.フォルダセレクタ用ダイアログが現れますので,ご希望のフォルダを選んでください.

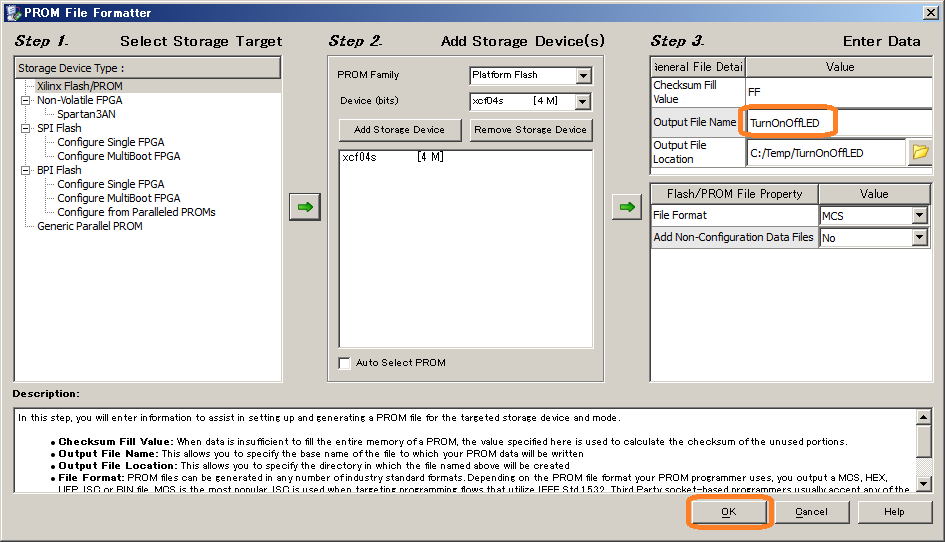

下図では出力するファイル名を指定しています.今回はTurnOnOffLEDという名前にしました.ファイル名を入力し終えましたら下のほうにあるOKボタンを押してください.

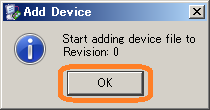

デバイスを追加することを確認するダイアログが現れますのでOKを押してください.

既に作成してある拡張子BINファイルを選択します.

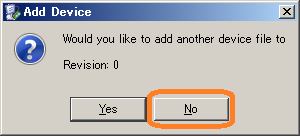

さらにもうひとつのデバイスを追加するか問い合わせられますが,今回は1個しかありませんのでNoボタンを押します.

これでデバイスの追加は終了です.数のようなダイアログが表れますのでOKボタンを押してください.

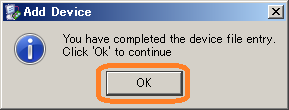

正しく設定が行えますと,下図のようにxcf04s(PROM)とxc6slx9(FPGA)が接続されているアイコンが現れます.確認しましたら,画面左下側にある「Generate File...」を選択し,MCSファイルを出力したのちに保存をしてください.

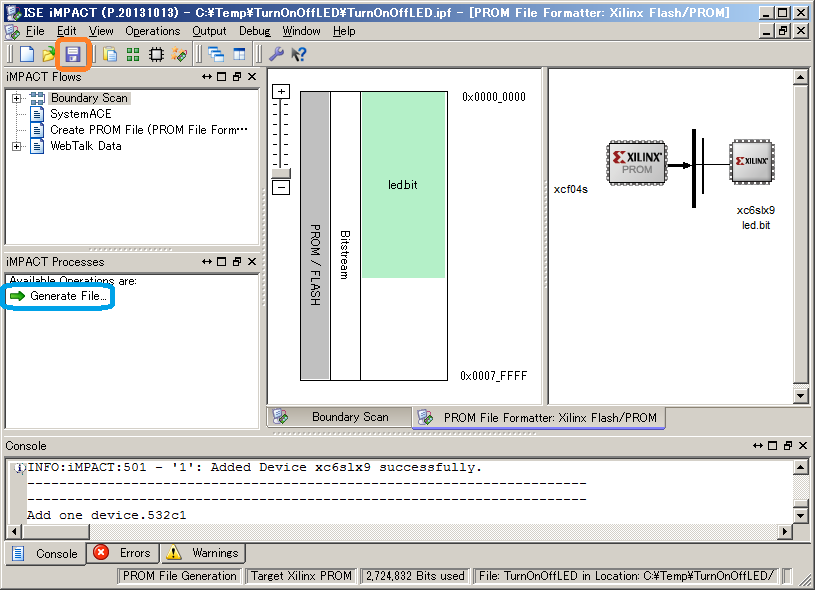

保存をするとき下図のようなダイアログが現れますのでOKを押してください.

以上でPROMに書き込むMCSファイルが作成されましたのでiMACTにそのファイルを追加しましょう.下の図のように,「Boundary Scan」タブを選択した後,空白箇所を右クリックすると現れるポップアップメニューから「Add Xilinx Device」を選択してください.

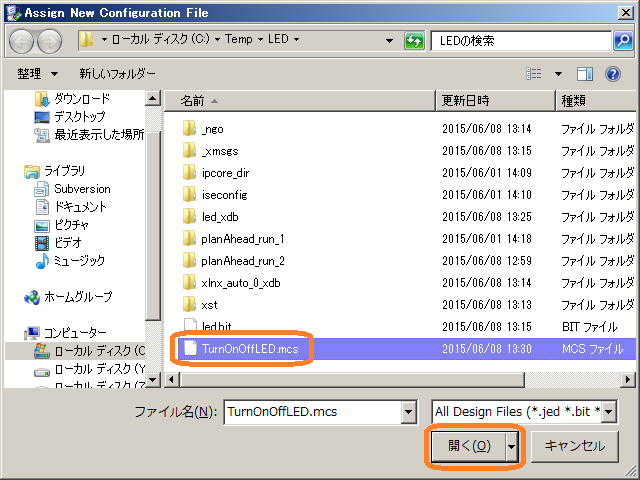

次にファイルセレクタが現れますので,先ほど作成したMCSファイルを指定します.

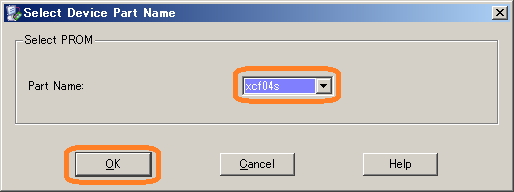

次にデバイスの部品名を聞かれます.今回使用しているEEPROMはXCF04Sですので,それを選択します.

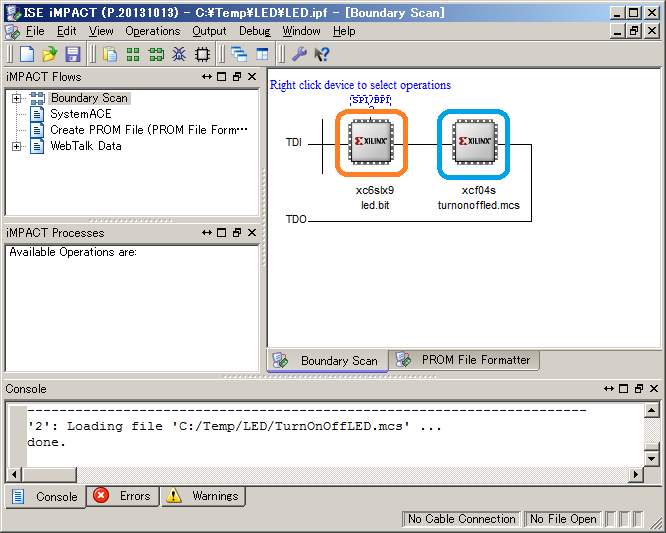

これでEEPROMへダウンロードすることができる状態になりました.下の図は左側(オレンジ)がFPGA,右側(青)がEEPROMを表しています.

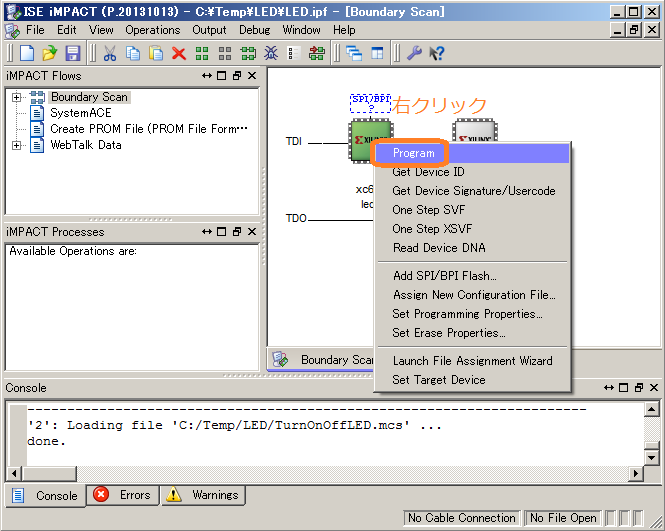

ダウンロードしたいデバイスを選択し,右クリックをすると下の図のようになりますので,「Program」を選んでください.下の例はFPGAへのダウンロードです.

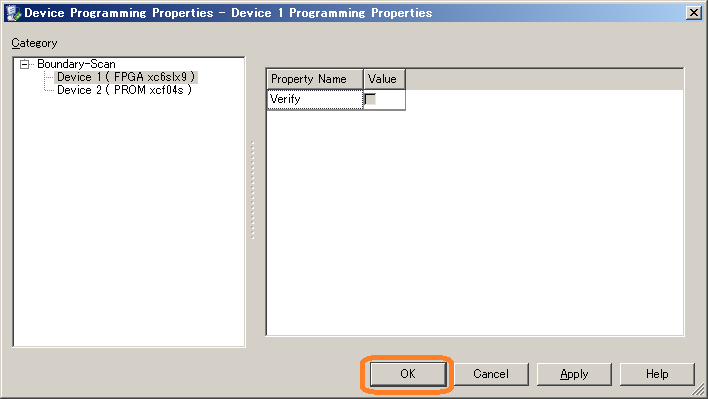

ダウンロードに先立ち,いくつかのオプションを選べますが,ここでは下図のようになにも選択しません.

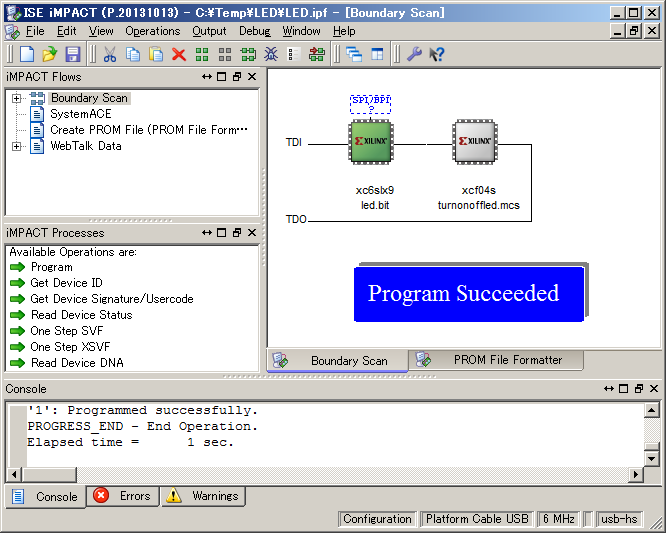

ダウンロードに成功すると下の図のように成功を表すメッセージが現れます.

ダウンロードに関して注意をしておきます.まず,EEPROMへのダウンロードは,その性質上,数に限りがあり,一定回数以上の書き込みを行うとEEPROMは壊れます.EEPROMへの書き込みは極力避けておいた方が無難です.

以上で,Xilix社製FPGAに回路を作成する手順の説明を終了します.やることが多いですので,わすれてしまったらこのページをもう一度読んでください.