タイミングチャート

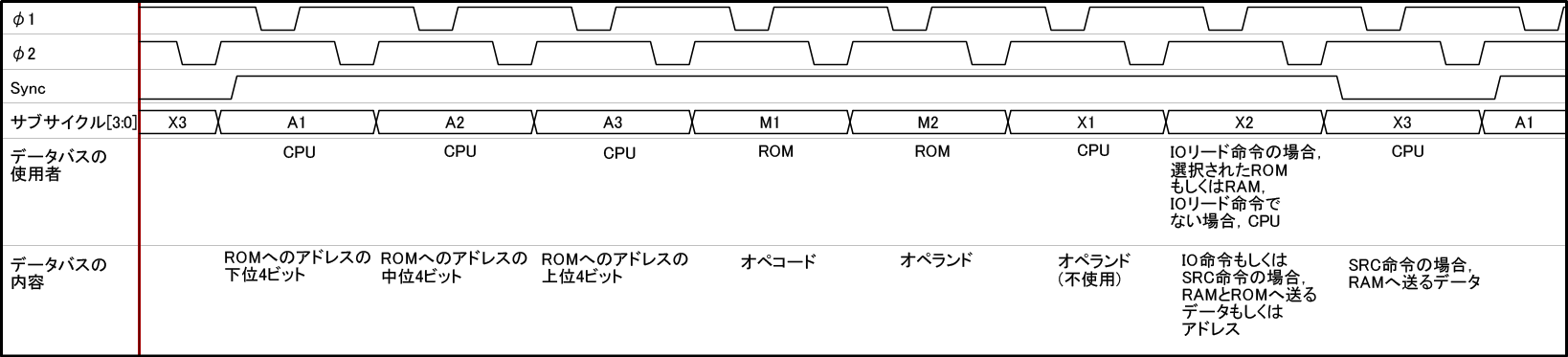

1サイクル内で行うことを理解するため,タイミングチャートを下に示します.Φ1の立ち上がりでバスの値を取りこみ,Φ2の立ち上がりで値を変化させます.ここではバスの値をを便宜上,A1~3,M1~2,X1~3で表すことにします.

ROMアドレス送信A1~3

MCS-4には4[bit]幅のバスしかないのに対し,ROMアドレスは12[bit]ですので,3個に分割して4004から4001にアドレスを送信します.その段階を上記のタイミングチャートではA1からA3で表します.メモリサブサイクルの行をご覧ください.A1からA3があるのが分かりますね.送信する順番はアドレスの下位4ビット(A1),中位4ビット(A2),上位4ビット(A3)となります.なお,A3で送られる4ビットは16個ある4001のチップそれぞれに設定されている固有の4ビットアドレスと対応しており,A3と同じ固有アドレスを持つ4001のみが反応するようになっています.

インストラクションコード受信M1~2

前述のROMアドレス送信の結果,ROMからのインストラクションコードを受信するのがM1とM2です.インストラクションコードは8[bit]であり,前半のM1でOPR,後半のOPA(オペランド)を受信します.OPAは4004だけでなく,現在インストラクションを読んでいるROM以外のROMにも送られます.また,IO関連のインストラクションの場合にはRAMにもオペランドが送られます.このように書くと,RAMがインストラクションをデコードしているように感じられますが,実際にはRAMはM2のときには常にOPAを受信しており,この後に行われるX1~X3の時にRAMがOPAを使うということです.IO関連のインストラクションの時にはRAMはOPAを無視するに過ぎません.

実行もしくはデータ送受信X1~X3

このサブサイクルでは,4004で演算を行ったり,RAMやROMに対してアドレスなどを送信したりします.X1からX3までの3クロックを使いますが,このうちX1では4004のバスから出力されるOPAは特に使われていません.X2ではI/Oのリード命令の場合には,選択されたROMもしくはRAMがバスを占有してCPUへデータを送り,それ以外の場合にはCPUがバスを占有します.X3ではCPUが占有し,RAMアドレスをRAMへ出力します.

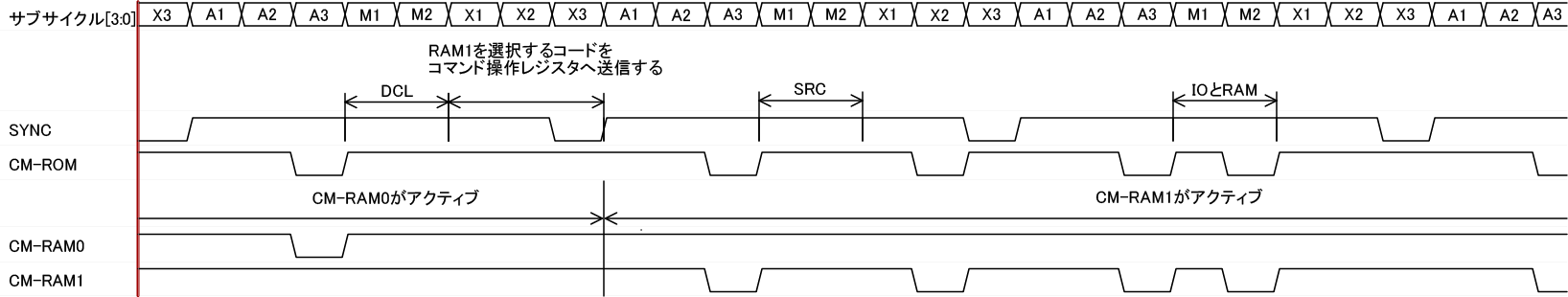

RAMやROMのタイミングチャート

下の図はRAMやROMとデータをやり取りするときのタイミングチャートです.この例ではRAM0グループに変えてRAM1グループをDCL命令で選択し,SRC命令でRAM1グループ内のRAMとそのRAMアレイ,さらにRAMアレイにあるメインメモリ文字を指定して,最後に入出力・RAM命令群の命令を実行しています.選択されているRAM群に対応するCM-RAMxのみ,A3でアサートされているのに加え,SRC命令ではX2,入出力・RAM命令群ではM2でもアサートされています.なお,すべてのCM-RAMxを論理積した信号をCM-ROMに送られています.