ここでは減算回路のリバースエンジニアリングについて説明します.すでに皆さんはセレクタ回路のリバースエンジニアリングを体験していますので,リバースエンジニアリングがどのようなものかは理解していると思いますし,ある程度慣れているものと思います.そこで,今回はなるべく回路構造を想像しながら行い,短時間で終えるようにしていきましょう.

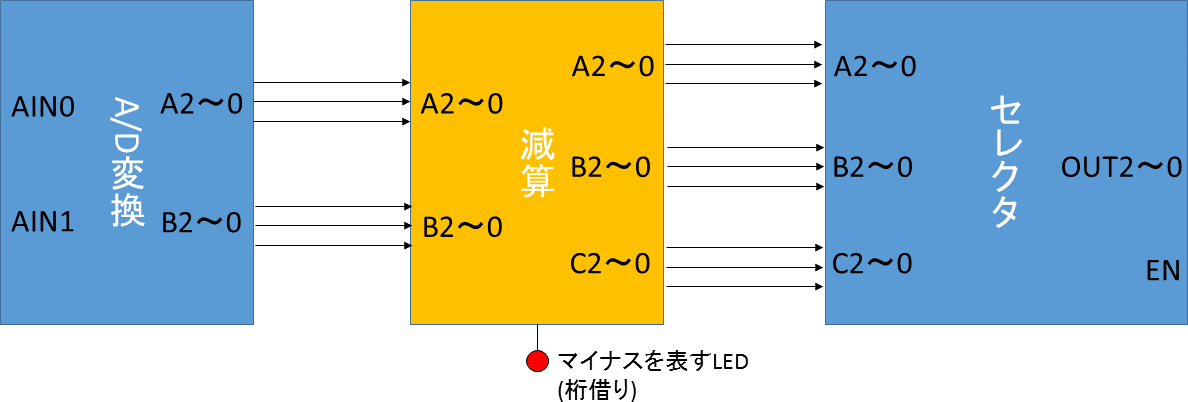

減算回路の役割

下図は減算回路のブロック図です.A/D変換回路からA2~A0(以下ではA)とB2~B0(以下ではB)の信号を入力され,セレクタ回路へA2~A0(A),B2~B0(B),C2~C0(以下ではC)の信号を出力しているのが分かるかと思います.減算回路ではA-Bを行い,その結果をCとしています.また,減算した結果桁借りが発生した場合のためのLEDが備わっています.

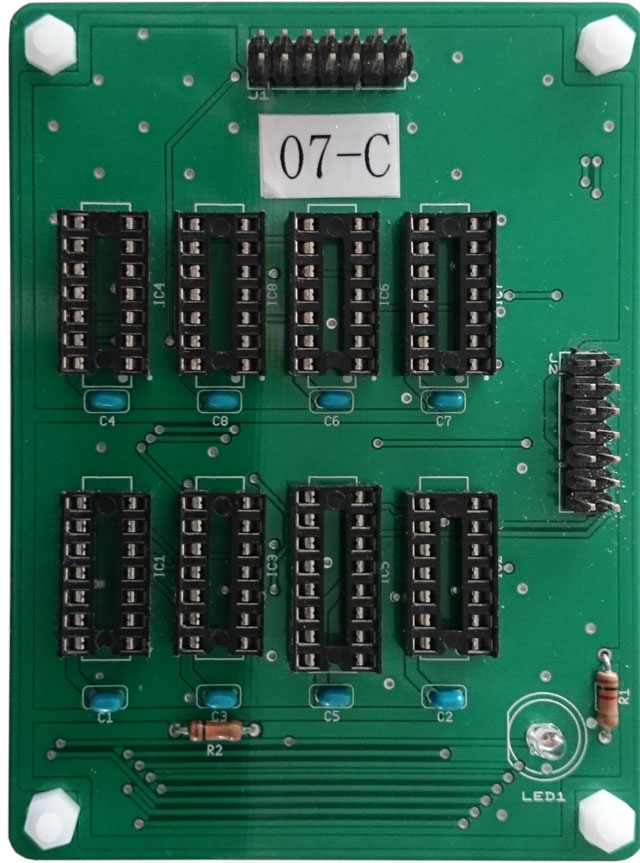

基板の外観

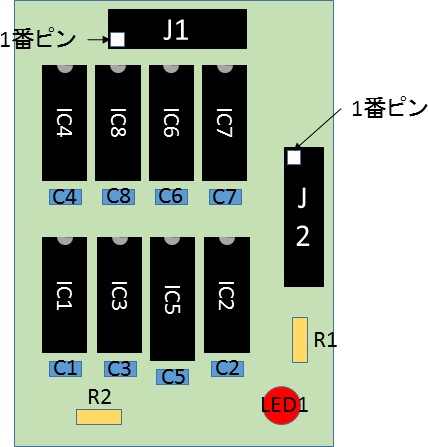

下に減算基板の外観を示します.使用するICは8個ありそのうちIC5は74LS83(4ビットフルアダー)であるため16ピンとなっています.J1はA/D変換からのコネクタであり,J2はセレクタへのコネクタです.基板の右下には桁借りを表すLEDがあります.

コネクタのアサイン

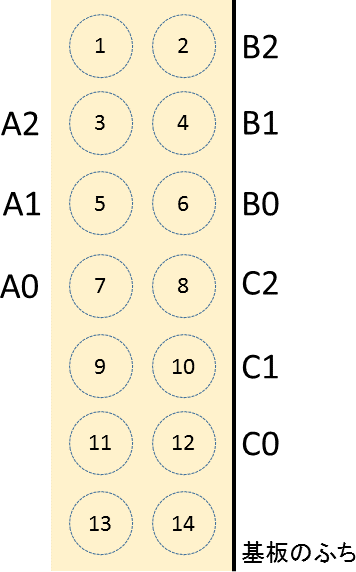

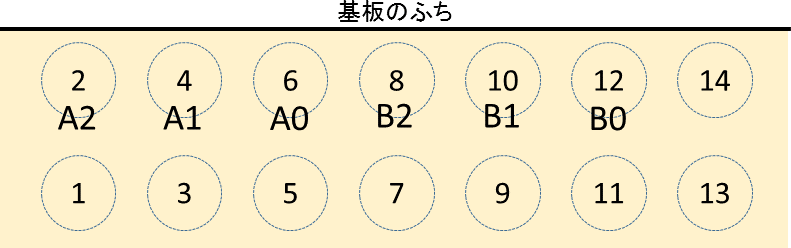

次にJ1およびJ2のピンアサインについて説明します.まずはJ1です.下の表はJ1のピンアサインです.A2~A0とB2~B0の6個が割り付けられています.それ以外の端子に何がつながっているかはテスタで調べてください.

| ピン番号 | 減算回路のJ1 |

| 1 | |

| 2 | A2 |

| 3 | |

| 4 | A1 |

| 5 | |

| 6 | A0 |

| 7 | |

| 8 | B2 |

| 9 | |

| 10 | B1 |

| 11 | |

| 12 | B0 |

| 13 | |

| 14 |

基板上でのアサインを下に示します.

次にJ2のピンアサインです.

| ピン番号 | 減算回路のJ2 |

| 1 | |

| 2 | B2 |

| 3 | A2 |

| 4 | B1 |

| 5 | A1 |

| 6 | B0 |

| 7 | A0 |

| 8 | C2 |

| 9 | |

| 10 | C1 |

| 11 | |

| 12 | C0 |

| 13 | |

| 14 |

基板上でのアサインを下に示します.

使用するIC

これまでのようにAND,OR,NOT,XORに加えて今回は4ビットフルアダーである74LS83を使用します.このICの詳細はデータシートを見てほしいのですが,簡単に説明すると書きのような特徴があります.

- 4ビットの加算が行えます.

- 下の桁の桁上がり(キャリ)を入力できます.

- 桁上がり(キャリ)を出力できます.

この加算器の使いどころがどこなのかが問題です.そのヒントは「2の補数」です.2の補数表現された信号を通常の数字に変えるときどのようなことをしたのか思い出してください.

IC1~IC8がどのICなのかまとめて下の表に示します.

| 部品名 | ICの種類 |

| IC1 | 74LS04(NOT) |

| IC2 | 74LS08(AND) |

| IC3 | 74LS08(AND) |

| IC4 | 74LS32(OR) |

| IC5 | 74LS83(4ビットフルアダー) |

| IC6 | 74LS86(XOR) |

| IC7 | 74LS86(XOR) |

| IC8 | 74LS86(XOR) |

報告事項

次に示す3点をレポートにまとめて報告してください.

- 減算回路の回路図

- 入力と出力の関係を示した真理値表

- 課題

- 減算基板の論理でなぜ減算ができるのか考察してください.

- 桁借り用LEDの動作について説明してください.

なお,Webの参考文献を挙げる場合には,信頼のできるページ,具体的には半導体メーカ,データシート,アプリケーションノートなどに限ります.ウィキペディアや個人的なブログを文献として挙げないようにしてください.