Page 3 of 4

IPの設定ウィザード

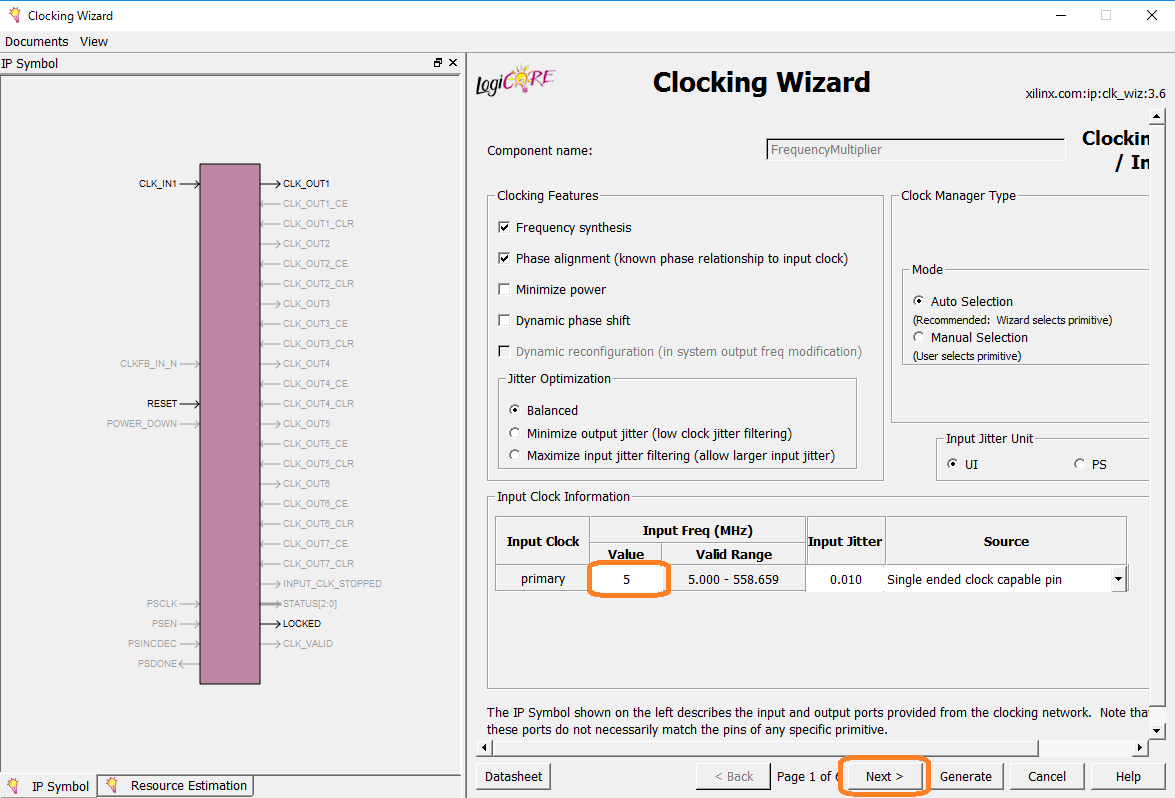

続いてClockの設定をするウィザードがはじまります.最初に入力するクロックの情報を設定します.ここでは最低5[MHz]の周波数となっておりますので,下図のように5と入力してください.

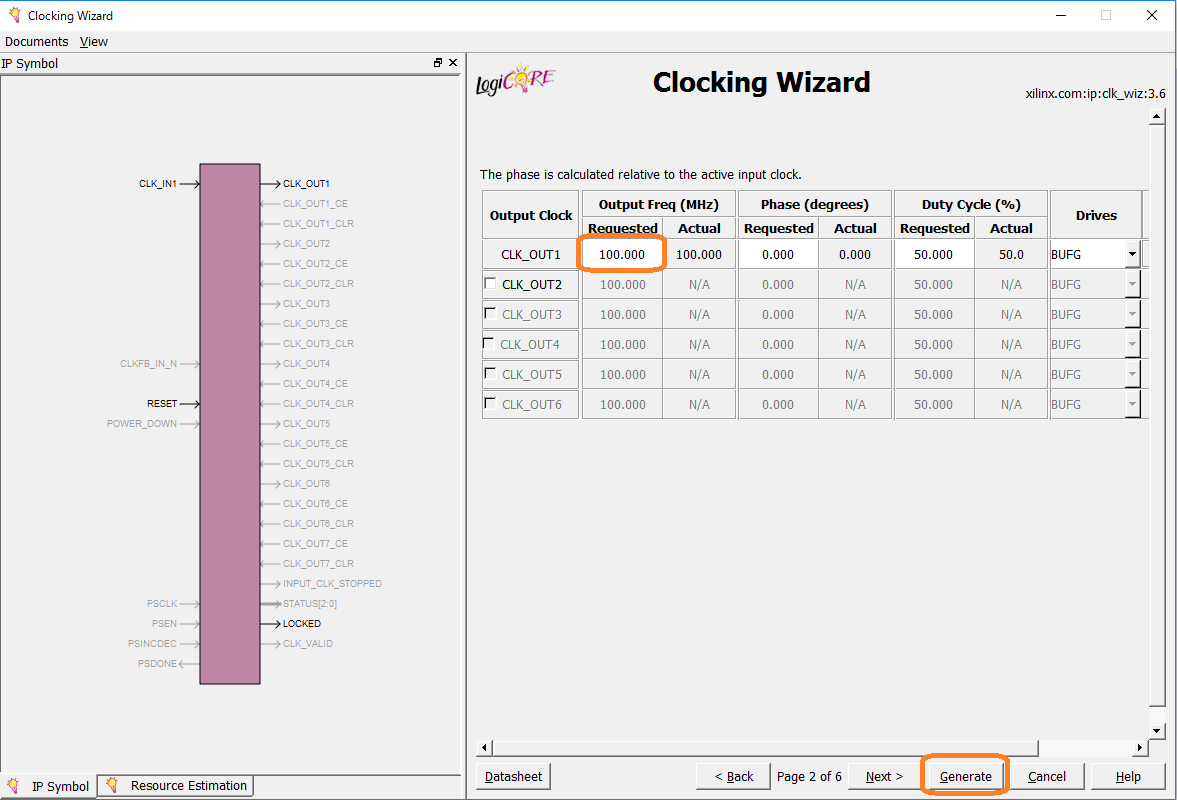

次に(というかこれで最後ですが),出力する波形の周波数を指定します.下図のように今回は100[MHz]とします.この後にまだ細かな設定を行えるのですがそこは省略します.そのためGenerateボタンを押します.

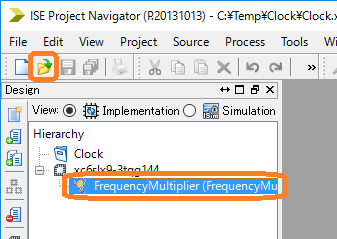

IPが生成されると下図のようになります.続いて,作成された回路を扱うためのVerilogファイルを開き,ポートを確認しておきましょう.下図のようにファイルオープンアイコンを押してください.

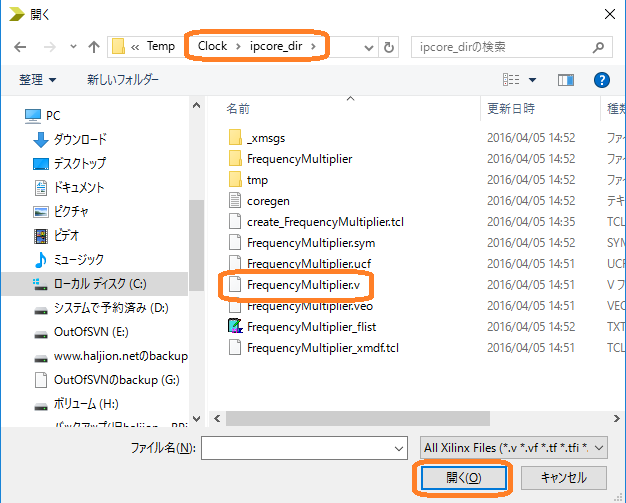

Clockフォルダの下にipcore_dirフォルダがあるはずです.その中にFrequencyMultiplier.vファイルがありますので選択して開くボタンを押しましょう.

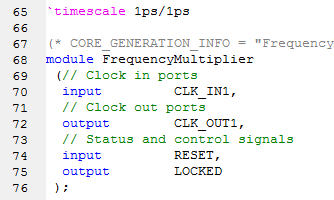

FrequencyMultiplier.vのポート宣言をご覧ください.下記のとおり,4種類のポートがあります.

今回生成されたポートの役割を下表にまとめておきます.

| ポート名 | 入力/出力 | 役割 |

| CLK_IN1 | 入力 | 入力されるソースクロック.5[MHz]を想定している. |

| CLK_OUT1 | 出力 | 出力されるクロック.100[MHz]を想定している. |

| RESET | 入力 | この信号がHighの時にはCLK_OUT1から何も生成されない. |

| LOCKED | 出力 | クロックが正しく出ているときにはHigh,そうでないときにはLowを出力. |