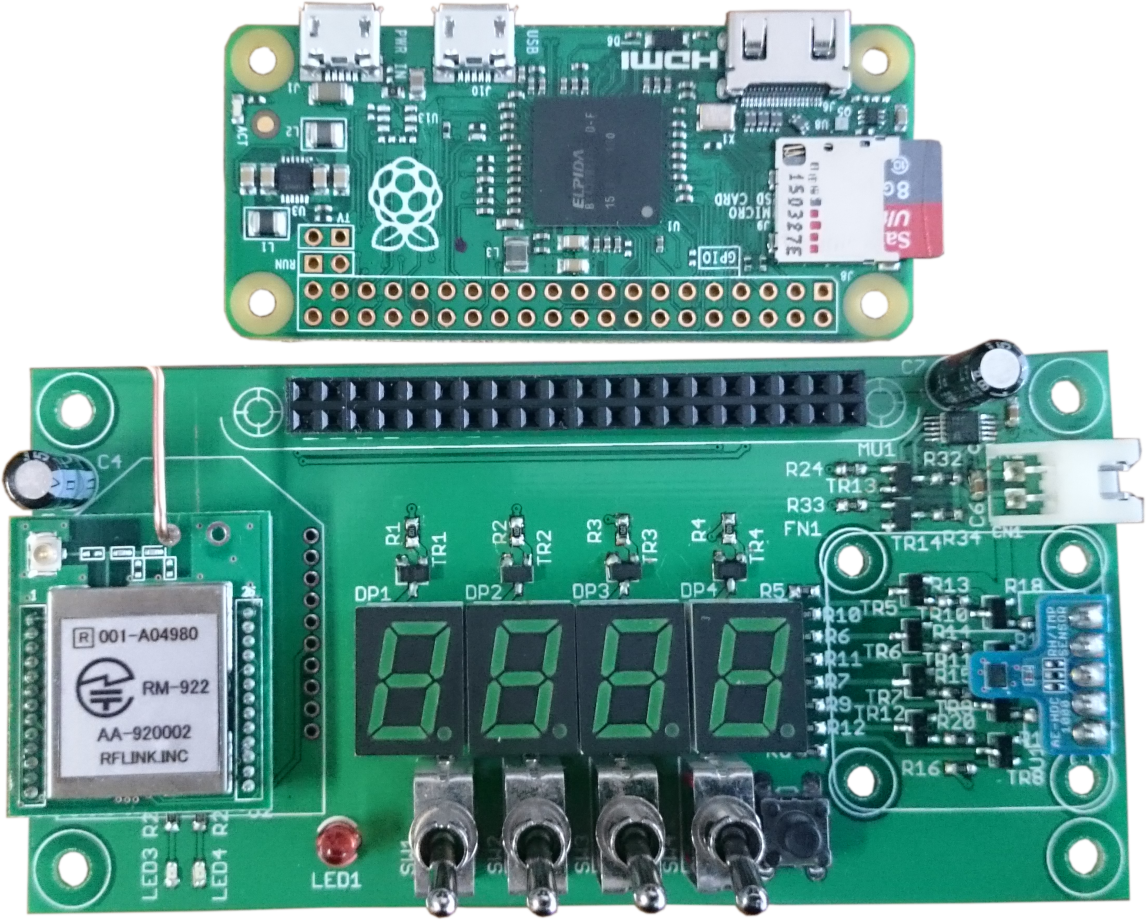

この文書では,教材に備わる4桁の7セグメントのピンアサインと制御方法について説明します.

1:概要

教材に備わる4桁の7セグメントは,各桁ごとに表示したい数値(4[bit])を入力すると,ダイナミック点灯方式で数字の表示をしてくれます.また,表示と非表示を切り替えることができます.

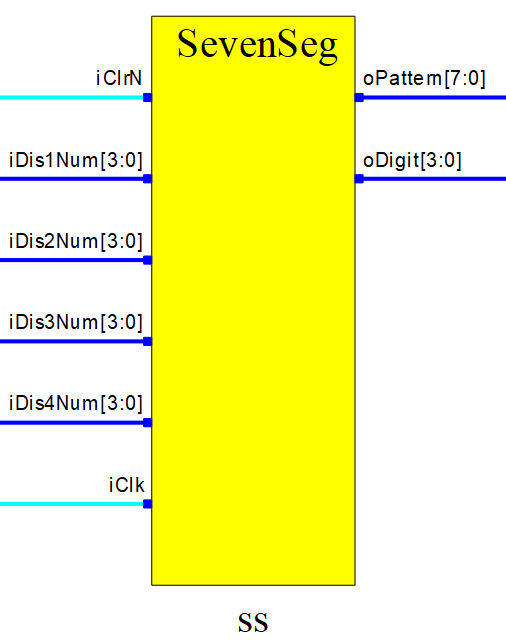

2:ブロック図

下にブロック図を示すとともに,各端子の説明を図の下にある表で示します.

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClrN | 入力 | 1 | 表示/非表示を切り替えるための端子です.Highだと点灯,Lowだと消灯です. |

| iDis1Num | 入力 | 4 | 教材のDP1と書かれている7セグメントLEDに表示される数字です. |

| iDis2Num | 入力 | 4 | 教材のDP2と書かれている7セグメントLEDに表示される数字です. |

| iDis3Num | 入力 | 4 | 教材のDP3と書かれている7セグメントLEDに表示される数字です. |

| iDis4Num | 入力 | 4 | 教材のDP4と書かれている7セグメントLEDに表示される数字です. |

| iClk | 入力 | 1 |

ダイナミック点灯方式で表示させるために使用されるクロック(27[MHz])です. |

| oPattern | 出力 | 8 | 表示したいパターン信号です.同じセグメント(たとえばセグメントA)は 電気的に接続されているため,もしDIGITが1111の場合にはすべてが同じ数字を 表示します.実際に使用するときには,上記DIGITは1個しかビットが立たないように 制御すれば,各桁は別の数字が表示されているように見えます. |

| oDigit | 出力 | 4 |

ダイナミック点灯方式では,4個の7セグメントLEDから1個を指定してから, |

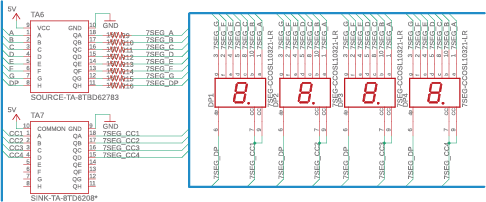

3:外部回路

下に7セグメントLEDに関する回路を抜き出した図を示します.左側にある2つのトランジスタアレイは,上がソース型,下がシンク型です.ソース型トランジスタアレイの出力が7セグメントLEDのアノード端子に接続されており,シンク型トランジスタアレイの出力が7セグメントLEDのカソード端子に接続されています.ソース型トランジスタアレイの入力にはA~G,DPの8端子があります.これらの端子をHighにすると7セグの各セグメントに接続されたアノード側へ電気が流れます.シンク型トランジスタアレイの入力端子をHighにすると7セグメントLEDのカソードから流れる電気をGNDへ接続されます.その結果,カソードコモンのLEDに電気が流れることになります.まとめますと,ソース型トランジスタアレイの入力端子をHighにするとアノードに電気が流れ,シンク型トランジスタアレイの入力端子をHighにするとカソードに電気が流れるということです.

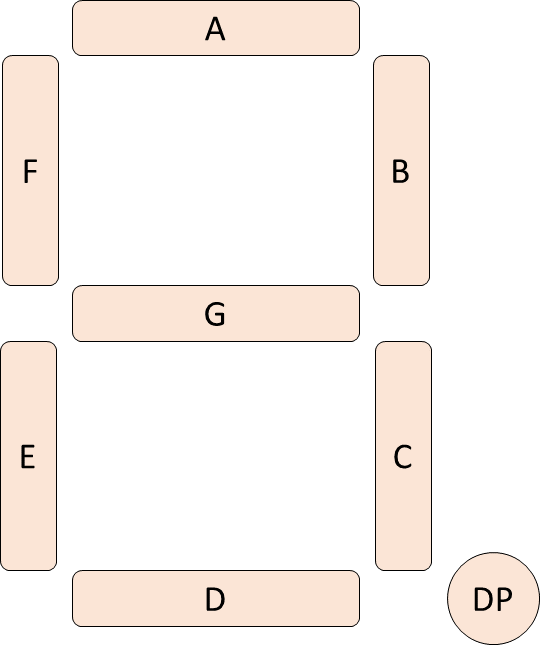

各セグメントは下図のように割り振られています.従いまして,DP4に「1」というパターンを表示する場合には,B,C,CC4をHigh,それ以外の端子をLowにすればよいのです.

4:ピンアサイン

ピンアサインを下表で示します.この表をもとにGOWIN EDA FloorPlannerでピンを割り振ってください.表示する数字を制御するためにトグルスイッチとプッシュスイッチを用いています.以前説明した7セグメントLEDを制御する回路のピンアサインでは,oDigitになっている4ビットの信号をCC1~CC4に,oPatternになっている8ビットの信号をA~G,DPに接続すればよいでしょう.

| ピン名 | 回路図上の名称 | FPGAのピン番号 | 信号の種類 | ポート名 |

| トグルスイッチ1 | SW1 | 69 | LVCMOS33 | iDis1Num[0] |

| トグルスイッチ2 | SW2 | 68 | LVCMOS33 | iDis1Num[1] |

| トグルスイッチ3 | SW3 | 57 | LVCMOS33 | iDis1Num[2] |

| トグルスイッチ4 | SW4 | 56 | LVCMOS33 | iDis1Num[3] |

| トグルスイッチ5 | SW5 | 55 | LVCMOS33 | iDis2Num[0] |

| トグルスイッチ6 | SW6 | 54 | LVCMOS33 | iDis2Num[1] |

| トグルスイッチ7 | SW7 | 53 | LVCMOS33 | iDis2Num[2] |

| トグルスイッチ8 | SW8 | 51 | LVCMOS33 | iDis2Num[3] |

| トグルスイッチ9 | SW9 | 42 | LVCMOS33 | iDis3Num[0] |

| トグルスイッチ10 | SW10 | 41 | LVCMOS33 | iDis3Num[1] |

| トグルスイッチ11 | SW11 | 35 | LVCMOS33 | iDis3Num[2] |

| トグルスイッチ12 | SW12 | 40 | LVCMOS33 | iDis3Num[3] |

| トグルスイッチ13 | SW13 | 34 | LVCMOS33 | iDis4Num[0] |

| トグルスイッチ14 | SW14 | 33 | LVCMOS33 | iDis4Num[1] |

| トグルスイッチ15 | SW15 | 30 | LVCMOS33 | iDis4Num[2] |

| トグルスイッチ16 | SW16 | 29 | LVCMOS33 | iDis4Num[3] |

| プッシュスイッチ | (不記載) | 3 | LVCMOS33 | iClrN |

| クロック | (不記載) | 32 | LVCMOS33 | iClk |

| セグメントA | A | 75 | LVCMOS33 | oPattern[0] |

| セグメントB | B | 74 | LVCMOS33 | oPattern[1] |

| セグメントC | C | 73 | LVCMOS33 | oPattern[2] |

| セグメントD | D | 72 | LVCMOS33 | oPattern[3] |

| セグメントE | E | 71 | LVCMOS33 | oPattern[4] |

| セグメントF | F | 70 | LVCMOS33 | oPattern[5] |

| セグメントG | G | 48 | LVCMOS33 | oPattern[6] |

| セグメントDP | DP | 49 | LVCMOS33 | oPattern[7] |

| DP1のカソードコモン | CC1 | 83 | LVCMOS33 | oDigit[0] |

| DP2のカソードコモン | CC2 | 84 | LVCMOS33 | oDigit[1] |

| DP3のカソードコモン | CC3 | 85 | LVCMOS33 | oDigit[2] |

| DP4のカソードコモン | CC4 | 86 | LVCMOS33 | oDigit[3] |

5:内部信号

4桁の7セグメントをダイナミック点灯方式で表示する場合,次に示す内部信号が必要となります.

| 名称 | reg/wire | ビット幅 | 個数 | 初期値 | 備考 |

| oPattern | reg | 8 | 1 | 8'b1111_1111 | ポート宣言の信号をregにしている. |

| oDigit | reg | 4 | 1 | 4'b0001 | ポート宣言の信号をregにしている. |

| cnt | wire | 2 | 1 | なし | 表示している桁を表す信号.0から3までの値となる. |

| dividedClk | wire | 1 | 1 | なし | およそ1.2[kHz]に分周されたクロック. |

| num | wire | 4 | 1 | なし | 表示する値. |

6: サブモジュール

ここでは7セグメントLEDを制御するために用いるサブモジュールについて説明します.サブモジュールとして下記の5つを用います.これらのサブモジュールを接続して一つのモジュールにしてください.

6-1: ダイナミック点灯用分周器

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClk | 入力 | 1 | 27[MHz]の入力クロック. |

| oDividedClk | 出力 | 1 | 1[kHz]に分周されたクロック. |

6-2: 表示桁用カウンタ

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClk | 入力 | 1 | 1[kHz]に分周されたクロック. |

| oCnt | 出力 | 1 | 0~3までの値.クロックが立ち上がるたびに数値が増える. |

6-3: 表示桁用セレクタ

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iDis1Num | 入力 | 4 | DP1に表示される0~15までの値. |

| iDis1Num | 入力 | 4 | DP2に表示される0~15までの値. |

| iDis1Num | 入力 | 4 | DP3に表示される0~15までの値. |

| iDis1Num | 入力 | 4 | DP4に表示される0~15までの値. |

| iCnt | 入力 | 2 | 上記4種の信号を選択する基準となる値.0: iDis1Num,1: iDis2Num,2: Dis3Num,3: Dis4Numを選択する. |

| oNum | 出力 | 4 | 選択された0~15までの値. |

6-4: 表示桁切替器

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iCnt | 入力 | 2 | 表示桁用カウンタで数えられた,0~3までの値. |

| oDigit | 出力 | 4 | 表示桁を1,非表示桁を0とする4ビットの値. |

6-5: 7セグメントLED用デコーダ

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClrN | 入力 | 1 | 0のときには非表示,1のときには表示する信号. |

| iNum | 入力 | 4 | 表示する0~15までの値. |

| iOnOff | 入力 | 1 | 隣の桁の残像を出さぬようにするため,0のときには非表示,1の時には表示にする信号.dividedClkと接続すればよい. |

| oPattern | 出力 | 8 | 7セグメントLED用にiNumをデコードしたもの. |