1:概要

チャタリングとは,スイッチの開閉時に発生するオンとオフの繰り返してしまう現象です.この期間はスイッチの種類によって異なり,たとえばタクトスイッチなどの場合には1[ms]以下,リレーなどの場合には10[ms]以下といわれています.CPU製作ボードにはいくつかのタクトスイッチがあり,1[ms]以下でオンとオフを繰り返す可能性があります.この文書では,およそ1[ms]以下のチャタリングをFPGAで防ぐ回路を作成する方法を説明します.

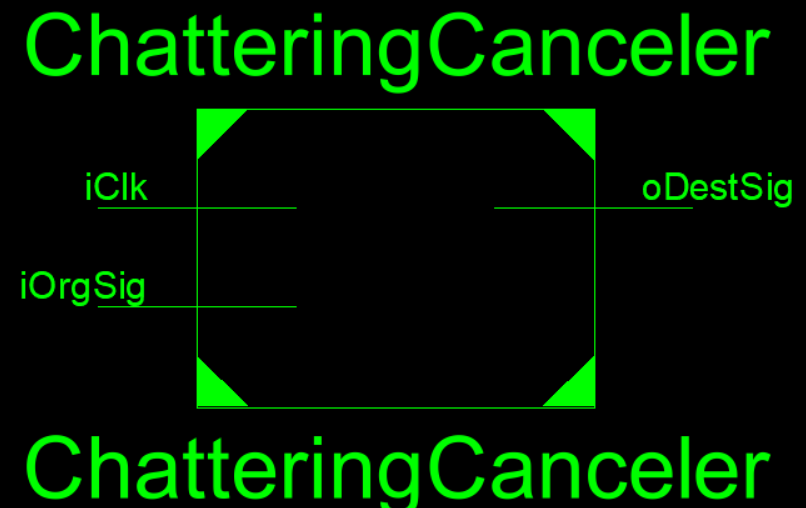

2:ブロック図(1個の信号用)

下の図がチャタリング防止回路のブロック図です.各端子の役割をその下の表に示します.

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClk | 入力 | 1 | 40[MHz]のクロックです. |

| iOrgSig | 入力 | 1 | チャタリングが起こっている信号です. |

| oDestSig | 出力 | 1 | チャタリングがなくなっている信号です. |

3:回路の概要(1個の信号用)

およそ1[ms]ごとに信号をラッチするということは,およそ1[kHz]の信号で入力信号をラッチすればよいということです.従って内部には40[MHz]を1220.703125[Hz](およそ1[kHz])に分周する回路を作成します.分周するには2x進カウンタを使うことになります.

問題

40[MHz]をおよそ1[kHz]にする分周器を作るとき2x(xは整数)進カウンタを作成することにします.xを求めてください.

1[kHz]の信号の立ち上がりエッジでiOrgSigをoDestSigとしてラッチして出力します.

4:内部信号(1個の信号用)

下記の内部信号が必要となります.

| 名称 | reg/wire | ビット幅 | 個数 | 初期値 | 備考 |

| cnt | reg | 15 | 1 | 15'b000_0000_0000_0000 | 32768進カウンタのための計数ようレジスタです. |

| oDestSig | reg | 1 | 1 | 1'b0 | ポートをregにしたものです. |

5:FPGAに作成する回路の構成(1個の信号用)

ここでは,作成する回路の概略を示します.

- 出力信号oDestSigをregとして作成します.

- 分周のためのカウンタcntを15ビットのregとして作成します.

- iClkが立ち上がりエッジのとき,次のことを行う回路を作成します.

-

- cntをインクリメントすします.

- もしcntが15'b111_1111_1111_1111であったら,次のことを行う回路を作成します.

- iOrgSigの信号をoDestSigへノンブロッキング代入します.

このようにすることで,およそごとに入力信号をラッチし,同時に出力します.

6:複数の入力信号

上記の回路では1個の信号のチャタリングを除去することができます.しかしCPUボードには18個のトグルスイッチが付いており,それらすべてのチャタリングを除去するようにした方が良いですよね?そこで複数の信号のチャタリングをとる回路に修正しようと思います.

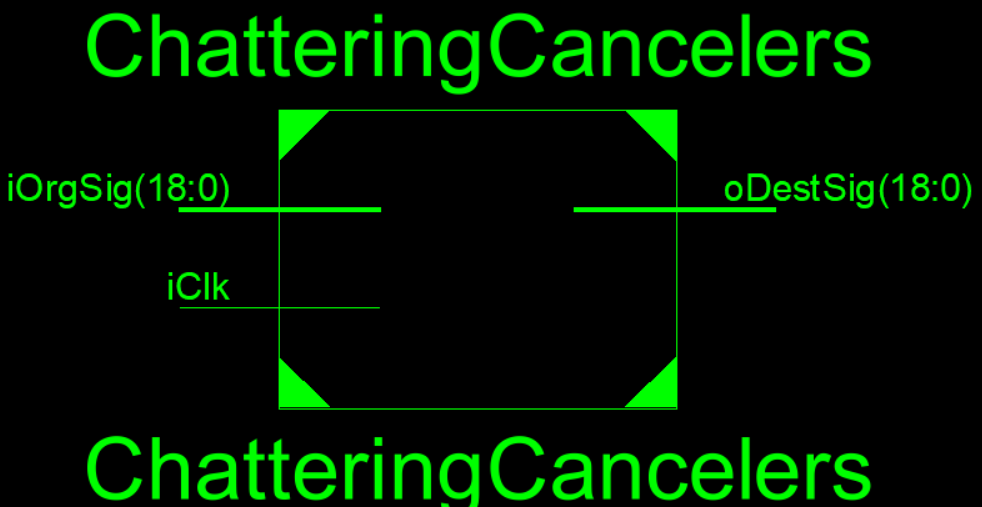

7:ブロック図(複数の信号用)

下のブロック図が複数の信号用チャタリング防止回路のブロック図です.各端子の役割をその下の表に示します.

| 端子名 | 入力/出力 | バス幅 | 説明 |

| iClk | 入力 | 1 | 40[MHz]のクロックです. |

| iOrgSig | 入力 | 19 | チャタリングが起こっている信号の集まりです. |

| oDestSig | 出力 | 19 | チャタリングがなくなっている信号の集まりです. |

8:回路の概要(複数の信号用)

基本的な考え方は1個の信号のチャタリングを防ぐ時と同じで,およそ1[kHz](正確にいうと1220.703125[Hz])ごとに値をラッチするようにします.違いは,一度に複数の信号をラッチするため,ラッチ用内部信号が複数になることぐらいです.

9:内部信号(複数信号用)

下記の内部信号が必要となります.

| 名称 | reg/wire | ビット幅 | 個数 | 初期値 | 備考 |

| cnt | reg | 15 | 1 | 15'b000_0000_0000_0000 | 32768進カウンタのための計数ようレジスタです. |

| oDestSig | reg | 19 | 1 | 19'b000_0000_0000_0000_0000 | ポートをregにしたものです. |

10:FPGAに作成する回路の構成(複数の信号用)

ここでは,作成する回路の概略を示します.

- 分周のためのカウンタcntを15ビットのregとして作成します.

- 出力信号oDestSigを19ビットのregとして作成します.

- iClkが立ち上がりエッジのとき,次のことを行う回路を作成します.

- cntをインクリメントすします.

- もしcntが15'b111_1111_1111_1111であったら,次のことを行う回路を作成します.

- iOrgSigをoDestSigへノンブロッキング代入します.

このようにすることで,およそ1[kHz]ごとに入力信号をラッチし,同時に出力します.