- はじめに

このページでは,Verilog で記述したHDLのコードをXilinx社製ISim(HDL用シミュレータ)でシミュレーションする方法について説明します. - 実行環境

・開発環境:ISE WebPACK 14.7

・シミュレータ:ISim 14.7 - Verilogのコード

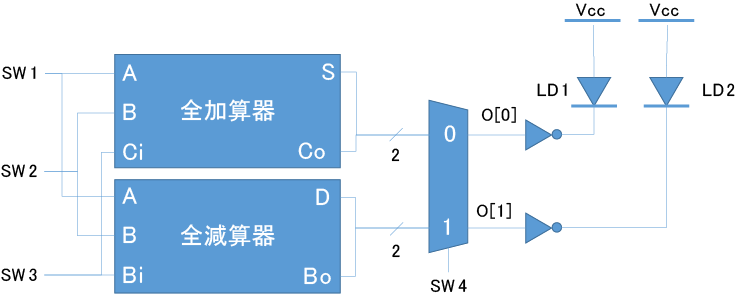

このページでシミュレーションをするにあたり,全加算器と全減算器が含まれるプロジェクトに対して行います.こちらに圧縮しておいておきます.ここにあるコードの内容は,SW1~SW3が全加算器と全減算器の入力,そしてその出力をSW4で切り替えてLD1とLD2に出力する回路となっています.下図にてブロック図を示します.

- プロジェクトファイルのオープンとテストベンチの追加

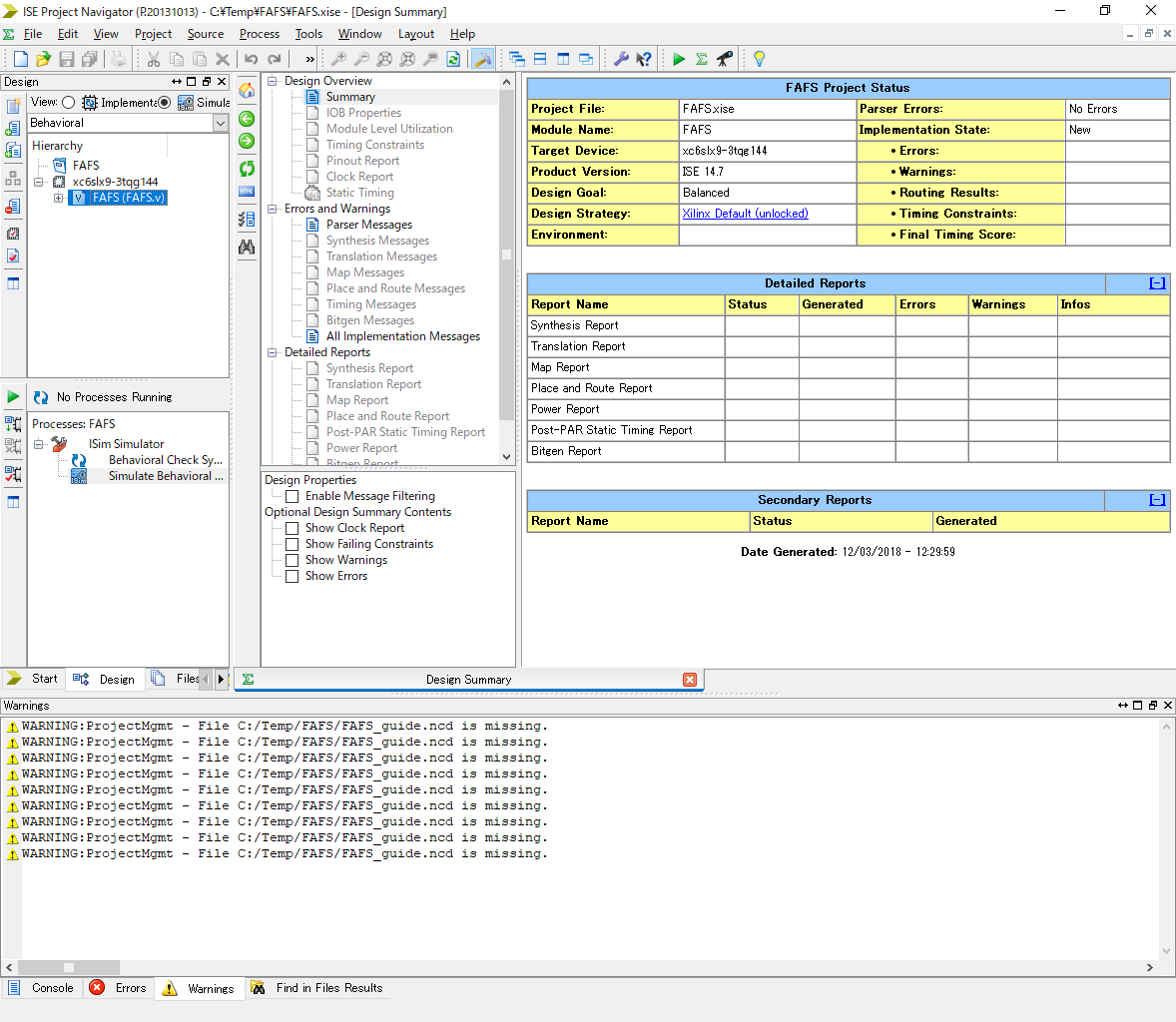

まずはコードが入っているプロジェクトを開きます.プロジェクトファイルであるFAFS.xiseファイルをダブルクリックすると下のようにISE WebPACKが起動します.

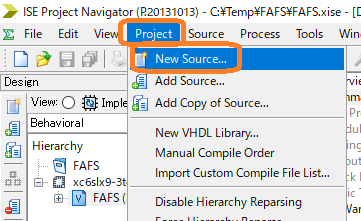

次にテストベンチを追加します.テストベンチの追加には,メニュー[Project]内にある[New Source...]を選択します.

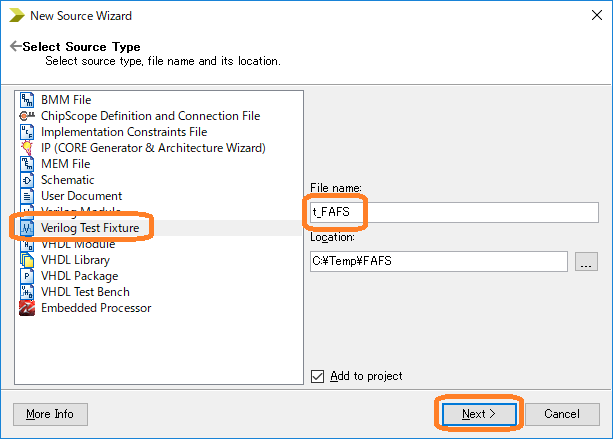

新しいソースとして,テストベンチを追加します.下図のように[Verilog Test Fixture]を選択し,さらにテストベンチ名をFile nameに記入します.テストベンチ名は何でもいいですが,この後にシミュレーションを行うFAFSモジュールに合わせ,ここではt_FAFSとしました.

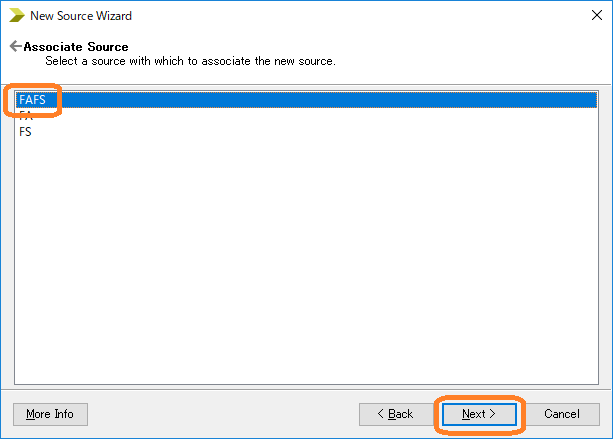

次にシミュレーションを行うモジュールを選択します.ここではFAFSに対してシミュレーションを行いたいので下図のようにそれを選択します.

最後に,ここまでで行ったテストベンチの概要が示されます.下図のように[Finish]を選択してください.

- テストベンチの記述

作成しましたt_FAFSにテストベンチを記述していきます.ここでは,SW1~SW3について,0と1を繰り返すようにし,SW4を0のままにするようなテストベンチを行います.SW4をそのままということなので,この場合には全加算器の動作が見られるはずです.下に作成したテストベンチを示します.網掛けしてある箇所が追記した箇所となっています.

module t_FAFS; // Inputs reg SW1; reg SW2; reg SW3; reg SW4; // Outputs wire LD1; wire LD2; // Instantiate the Unit Under Test (UUT) FAFS uut ( .SW1(SW1), .SW2(SW2), .SW3(SW3), .SW4(SW4), .LD1(LD1), .LD2(LD2) ); integer i,j,k; initial begin // Initialize Inputs SW1 = 0; SW2 = 0; SW3 = 0; SW4 = 0; // Wait 100 ns for global reset to finish #100; // Add stimulus here for(i=0; i<2; i=i+1) begin for(j=0; j<2; j=j+1) begin for(k=0; k<2; k=k+1) begin #10 SW1 = SW1 + 1'b1; end SW2 = SW2 + 1'b1; end SW3 = SW3 + 1'b1; end end endmodule - ISimの起動

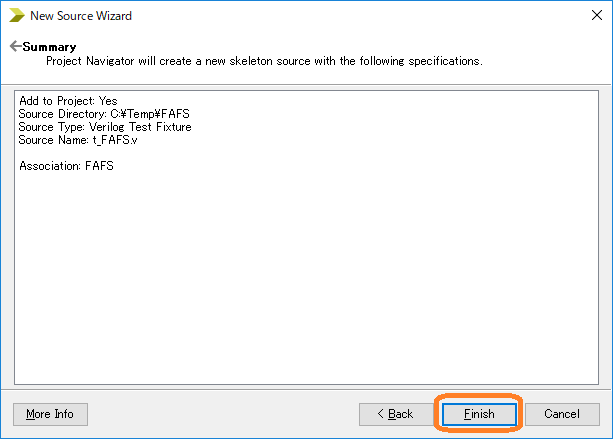

では,作成したテストベンチを動かしてみましょう.下図のように[Simulation]ラジオボタンを選択,テストベンチを選択,そして[Simulate Behavioral Model]を選択します.

- シミュレーションの実行

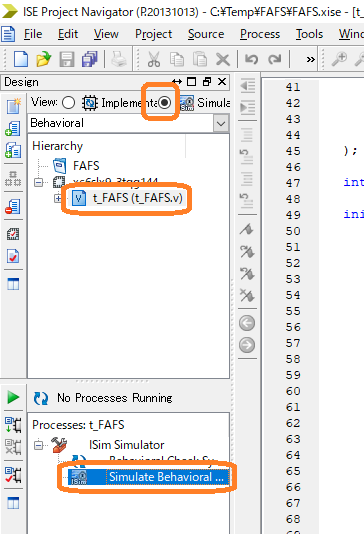

ISimが立ち上がると下の図のようになります.このうち,シミュレーションの実行を行うためのアイコンは上側に集中しています.

実行に関するアイコンを拡大したものを下に示し,左から順番に説明していきます.

・Restart:シミュレーションを最初からやり直す前に押されます.

・Run All:止められるまでずっと実行します.

・Run for the time:このアイコンの右側にある時間だけ実行されます.

・Step:テストベンチを一行ずつ実行されます.

・Break:Run Allで実行するとずっと実行し続けますが,それをいったんやめられます.上記の図ではRun Allをしていないのでインアクティブになっています.

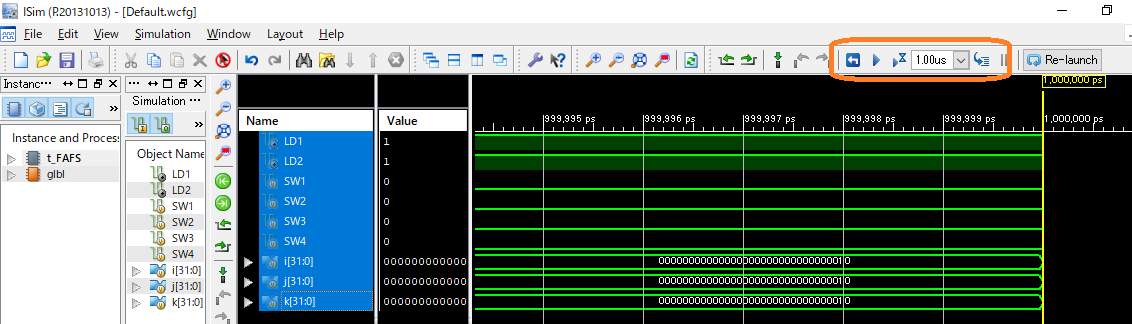

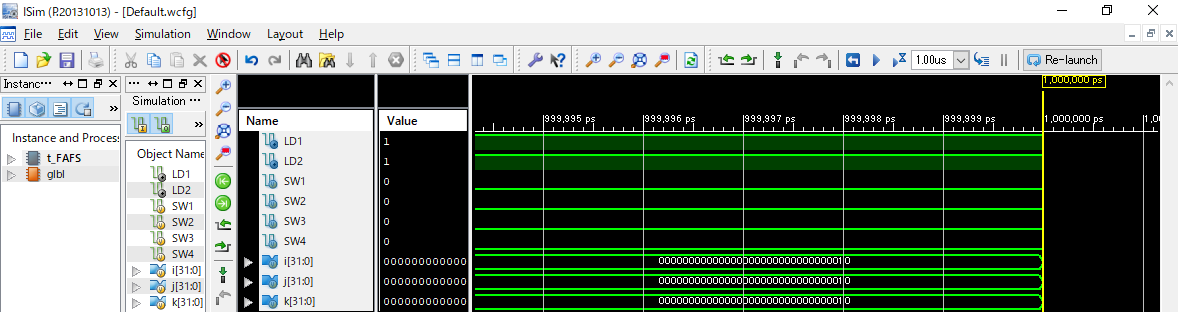

ここの例では1[us]実行させてみます.従って,まずは[Restart]を押して,そののちに[Run for the time]を押してください.その結果,下の図のようになるはずです.

さて,これでは見たい100[ns]~200[ns]あたりが見えません.見たいところを中心に見るには下図に示すアイコンを使います.これらは画面上部にあります.

左から順番に説明していきます.

・Zoom In:拡大します.

・Zoom Out:縮小します.

・Zoom to Full View:全体を見られるようにします.

・Zoom to Cursor:カーソルで選択した箇所を拡大します.

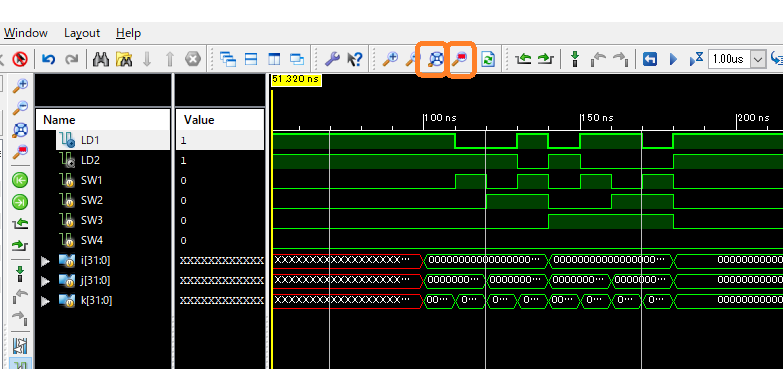

ここでは,Zoom to Full Viewを押したのち,Zoom to Cursorを使って100~200[ns]付近を選択します.SW1~SW3が変化するに従い,LD1(全加算器のS)とLD2(全加算器のCo)が変化している様子が分かります.

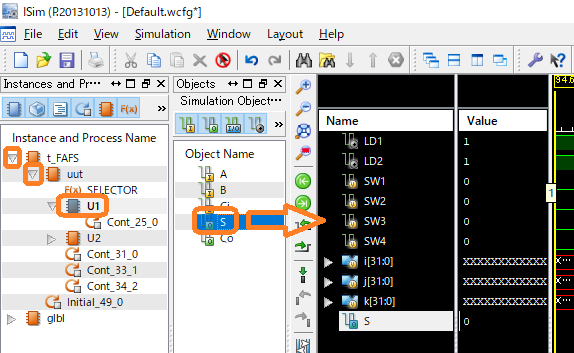

- 内包しているモジュールにある信号の追加

最後に,内容しているモジュールの信号を見る方法について説明します.デバック中に内包しているモジュールの挙動を確認したいときがあります.そのようなときに使えるテクニックです.ここでは全加算器のSの信号を見ようと思います.下図のように,左側ウィンドウ内にある[t_FAFS]の左側の三角アイコンを押すと,t_FAFSの階層構造が見られます.さらに[uut]の左側三角アイコンを押し,その中にある[U1]をクリックするとU1に含まれる信号が見えます.ここでは[S]を見たいのでこれをタイミングチャートの方へドラッグアンドドロップしてください.その結果が下の図です.

このままではSの信号が現れません.先ほど説明した手順に従い,シミュレーションを再度実行してください.そうすると,Sの信号が見られるはずです.

以上のようにシミュレーションをし,より簡単にデバックしていきましょう.

ISimの使い方

- Details

- Written by: 芦田和毅